当设计一个USB 电路板时,需要重点关注

D+/D-:高速差分信号,容易受到外界噪声的干扰,影响信号的传输质量。

供电信号VBUS:供电信号引脚上的电源纹波会对数据传输信号产生很大的干扰,因此必须经过滤波。而且接地信号也要经过滤波,减少干扰。对于大电流负载也要注意电压跌落。

PCB Latout 注意

D+/D-等长控制:当工作在高速模式或者USB3.0速率时,需要保证D+/D-等长布线。D+和D–走线的长度差异不应超过50 mil(1.25 mm),从而可以避免信号时滞并防止对交变电压产生影响

D+和D–走线的长度要小于3 英寸(75 mm)。推荐两条走线长度不大于1 英寸

布线中,应将直角进行两次45°的弯曲或变成圆角(而不是90°的直角弯曲)

阻抗控制:D+/D-差分布线,阻抗控制90Ω±10%

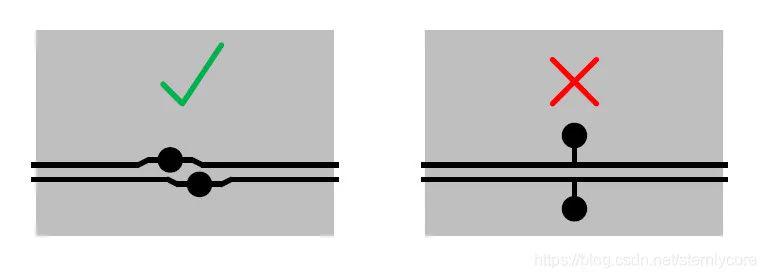

No Stub(无支点):当增加测试点或一些器件时,尽量保证差分信号无支点,如下示意:

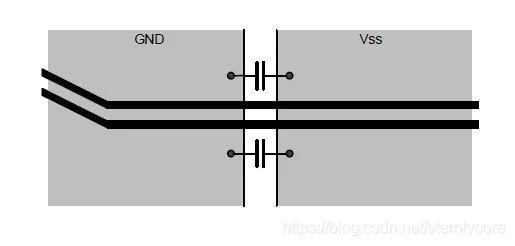

完整参考平面:D+/D-阻抗实现需要完整参考平面,不能出现分裂参考平面。如果不得以出现分离参考平面,需要连接跨接电容,如下示意:

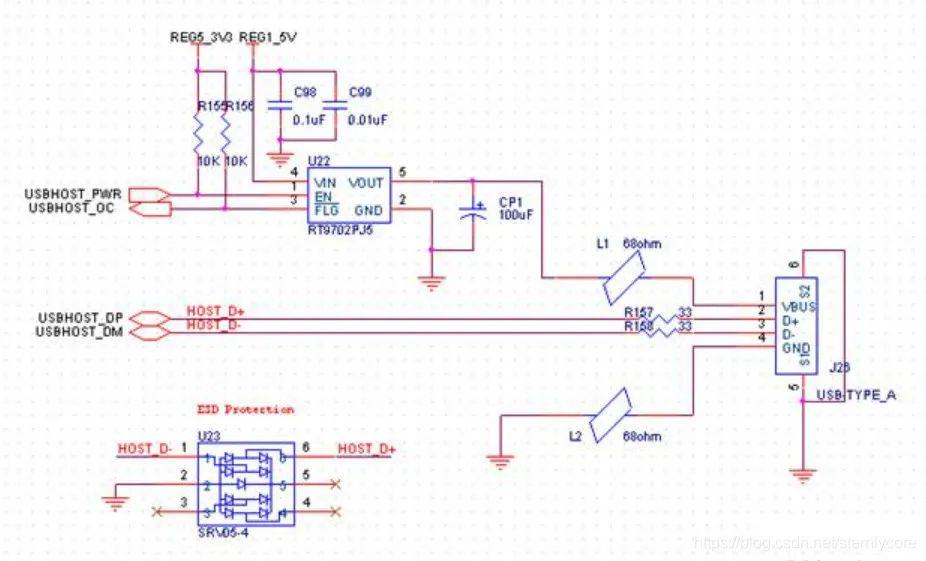

原理设计

现在芯片集成度很高,USB_Host外围设计比较简单,如下示意:

USB控制器信号:USB_PWR,DP,DM,USB_OC,USB_VBUS

限流器件:RT9702,USB2.0规范负载从VBUS最高索取500mA电流,超过500mA会关断

静电保护:SRV05 防止静电把连接器信号打坏,靠近USB接口放置

磁珠L1/L2:消除电源信号上的高频噪声,增强抗抖动性能。磁珠的电阻值介于47ohm至1000ohm之间(100MHz信号频率时),靠近连接器放置

R157/R158:匹配电阻,防止信号过冲,阻值一般在10Ω-33Ω之间,靠近USB控制器放置

CP1:大电容保证插拔瞬间或大数量数据传输时导致VBUS电压跌乱过大,靠近USB接口放置

版权声明:本文为CSDN博主「sternlycore」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/sternlycore/article/details/88547682