上一篇简单介绍了LPDDR4的特性,本文结合实际SOC(TI的TDA4)介绍一下LPDDR4(Micron的MT53D1024M32D4DT-046AAT:D)的硬件设计,包括原理图和PCB。

原理图设计

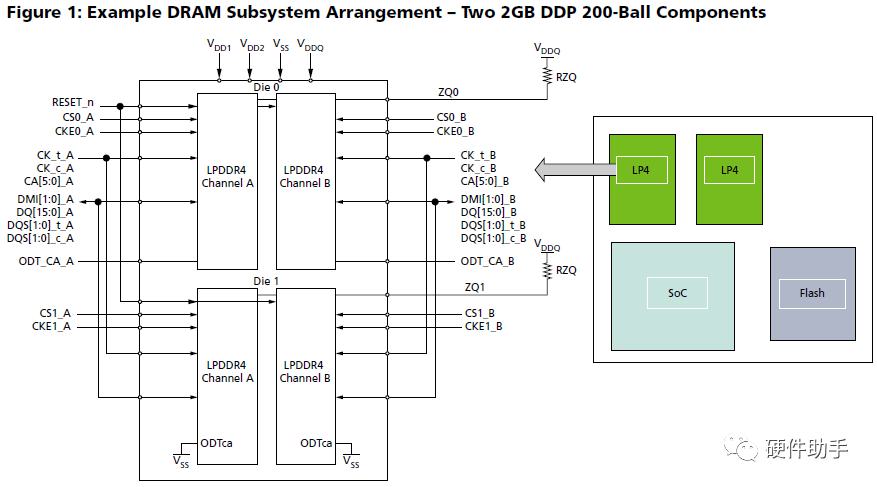

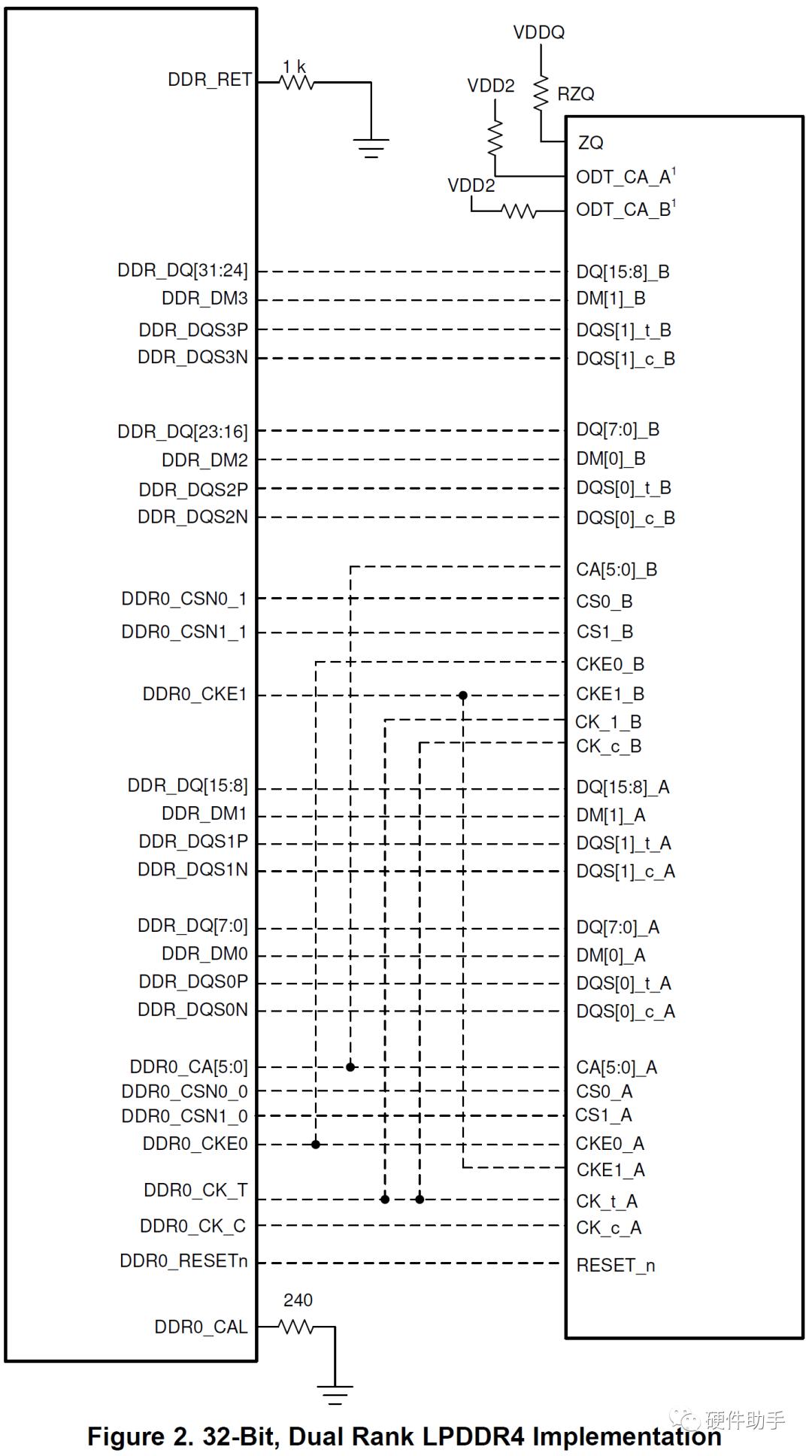

LPDDR4的框图如下:

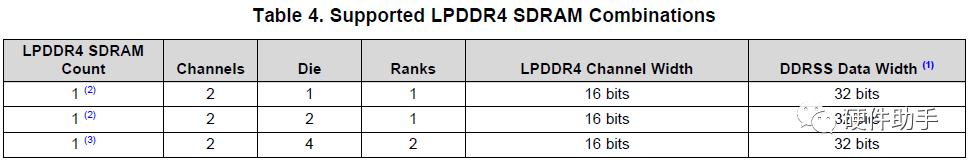

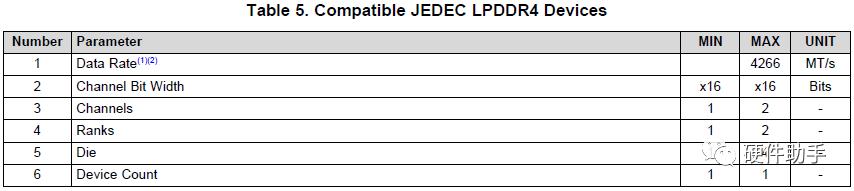

SOC的DDRSS接口如下:

TDA4的DDR控制器支持32bit数据。

PCB设计

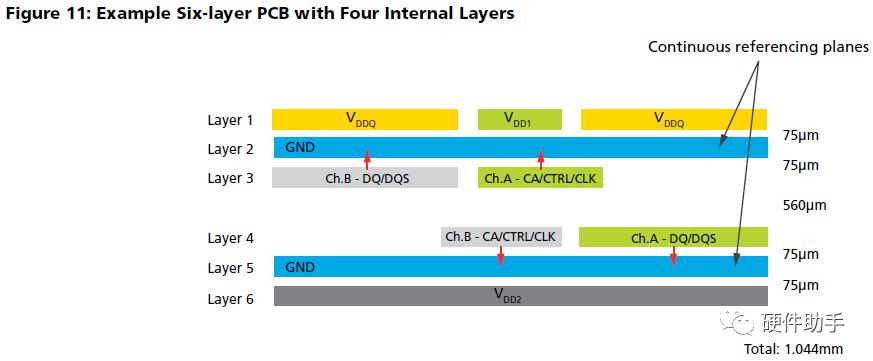

叠层部分,由于SOC信号较多,推荐10层板,详细如下:

而LPDDR4则从SI和PI的角度考虑,推荐至少6层板。

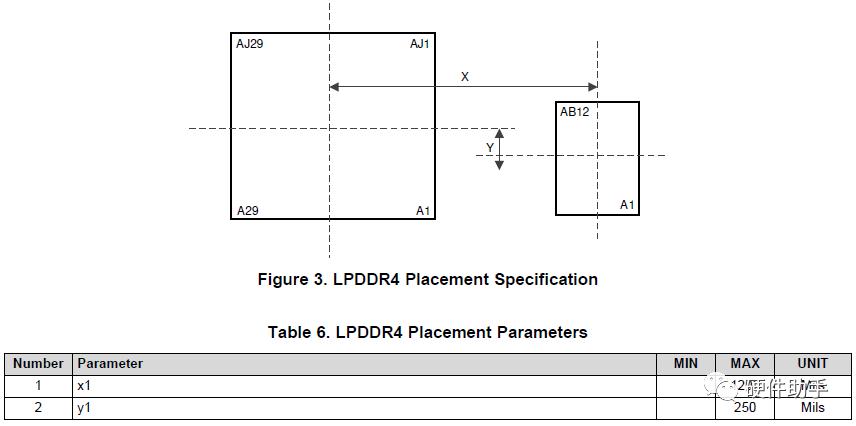

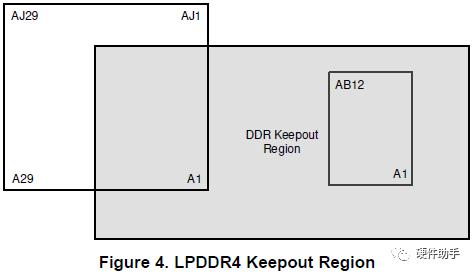

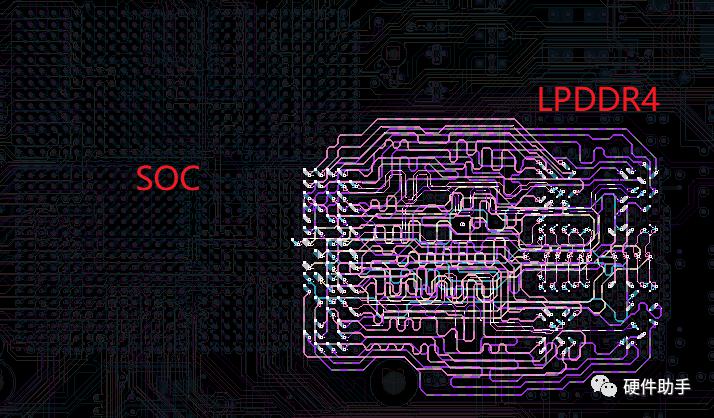

SOC推荐的LPDDR4布局方式如下:

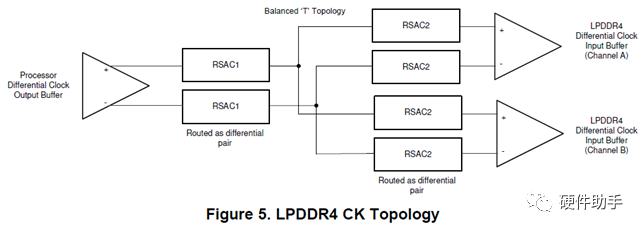

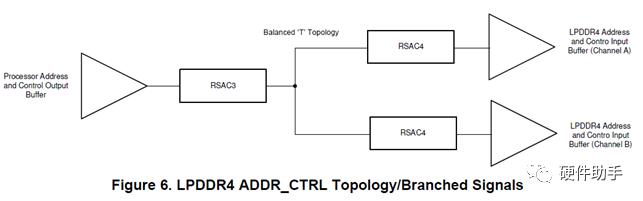

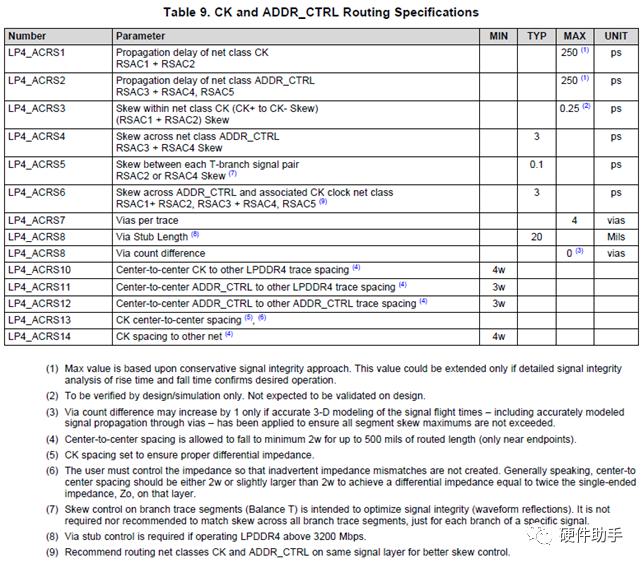

CK和ADDR_CTRAL采用平衡T型拓扑布线。

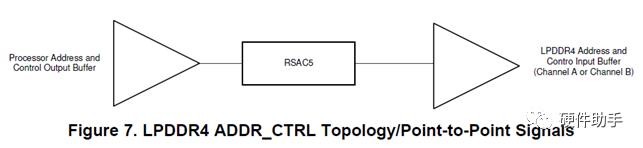

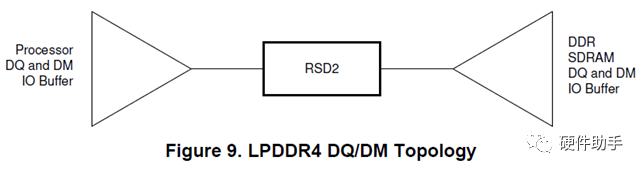

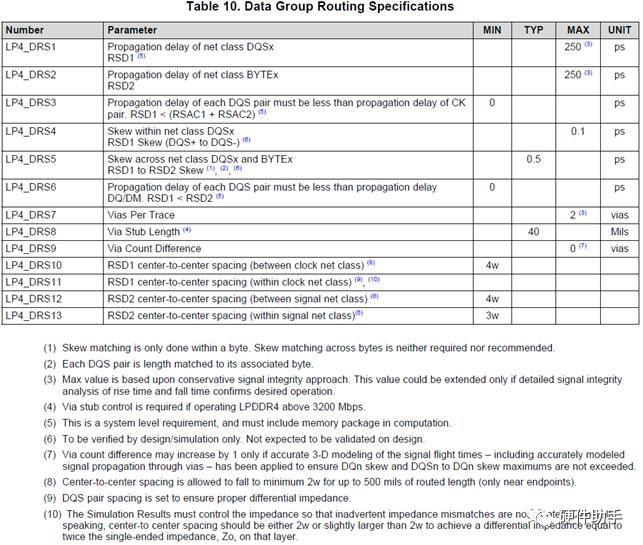

DQ采用点对点布线。

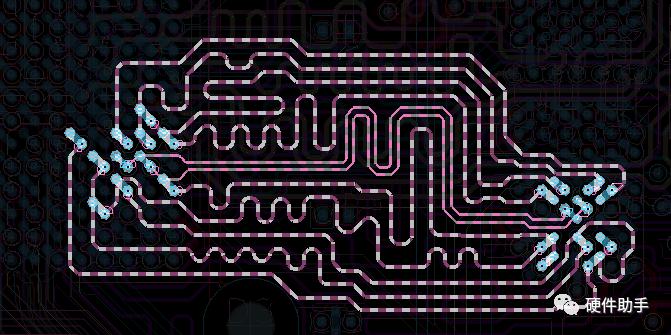

布线完成的PCB如下:

CK和ADDR_CTRAL的布线如下:

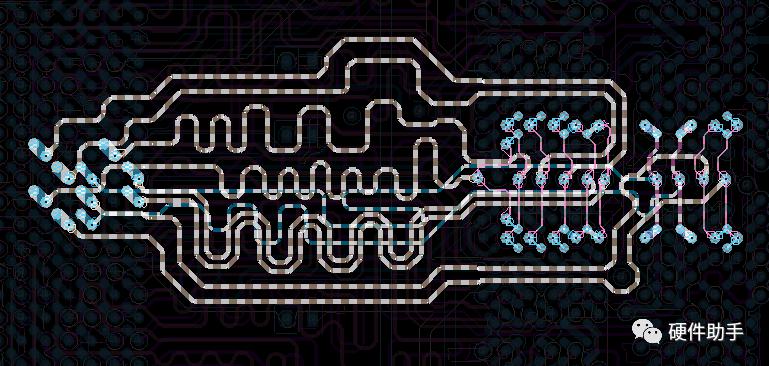

数据组的布线如下:

以上就是针对LPDDR4的原理图和PCB设计,由于速率比较高,达到4266Mbps,实际设计过程中需要进行仿真,同时在板材选择、背钻等方面需要进行特殊设计。