ж—ҘзӣҠеҸ‘еұ•зҡ„жҠҖжңҜеҜ№иҠҜзүҮз”өеҺӢжөӢиҜ•зҡ„жҢ‘жҲҳ

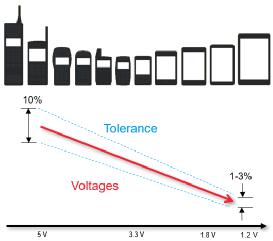

йҡҸзқҖ5GгҖҒиҪҰиҒ”зҪ‘зӯүжҠҖжңҜзҡ„йЈһйҖҹеҸ‘еұ•пјҢдҝЎеҸ·зҡ„дј иҫ“йҖҹеәҰи¶ҠжқҘи¶Ҡеҝ«пјҢйӣҶжҲҗз”өи·ҜиҠҜзүҮзҡ„дҫӣз”өз”өеҺӢйҡҸд№Ӣи¶ҠжқҘи¶Ҡе°ҸгҖӮж—©жңҹиҠҜзүҮзҡ„дҫӣз”өйҖҡеёёжҳҜ5Vе’Ң3.3VпјҢиҖҢзҺ°еңЁй«ҳйҖҹICзҡ„дҫӣз”өз”өеҺӢе·Із»ҸеҲ°дәҶ2.5VгҖҒ1.8VжҲ–1.5VпјҢжңүзҡ„иҠҜзүҮзҡ„ж ёз”өеҺӢз”ҡиҮіеҲ°дәҶ1VгҖӮиҠҜзүҮзҡ„дҫӣз”өз”өеҺӢи¶Ҡе°ҸпјҢз”өеҺӢжіўеҠЁзҡ„е®№еҝҚеәҰд№ҹеҸҳеҫ—и¶ҠиӢӣеҲ»гҖӮеҜ№дәҺиҝҷзұ»дҫӣз”өз”өеҺӢиҫғе°Ҹзҡ„й«ҳйҖҹиҠҜзүҮзҡ„з”өеҺӢжөӢиҜ•з”Ёз”өжәҗеҷӘеЈ°иЎЁзӨәпјҢжөӢжұӮиҰҒжұӮд»ҺВұ5%еҲ° Вұ-1.5%пјҢд№ғиҮіжӣҙдҪҺгҖӮ

еҰӮжһңиҠҜзүҮзҡ„з”өжәҗеҷӘеЈ°жІЎжңүиҫҫеҲ°и§„иҢғиҰҒжұӮпјҢе°ұдјҡеҪұе“Қдә§е“Ғзҡ„жҖ§иғҪпјҢд№ғиҮіж•ҙжңәеҸҜйқ жҖ§гҖӮеӣ жӯӨе·ҘзЁӢеёҲйңҖиҰҒеҮҶзЎ®ең°жөӢйҮҸзҺ°д»Јз”өи·Ҝдә§е“Ғдёӯзҡ„иҠҜзүҮз”өеҺӢзҡ„з”өжәҗеҷӘеЈ°гҖӮ2 иҠҜзүҮз”өжәҗеҷӘеЈ°зҡ„зү№зӮ№

2.1 жӣҙе°Ҹе№…еәҰпјҢжӣҙй«ҳйў‘зҺҮ

2.1 жӣҙе°Ҹе№…еәҰпјҢжӣҙй«ҳйў‘зҺҮд»ҘеҫҖз”өжәҗеҷӘеЈ°зҡ„иҰҒжұӮз»ҙжҢҒеңЁеҮ еҚҒmVзҡ„йҮҸзә§пјҢиҖҢйҡҸзқҖиҠҜзүҮз”өеҺӢзҡ„йҷҚдҪҺпјҢеҫҲеӨҡиҠҜзүҮзҡ„з”өжәҗеҷӘеЈ°е·Із»ҸеҲ°дәҶmVзҡ„йҮҸзә§пјҢжҹҗдәӣз”өжәҗж•Ҹж„ҹзҡ„иҠҜзүҮиҰҒжұӮз”ҡиҮіеҲ°дәҶзҷҫuVзҡ„йҮҸзә§гҖӮзӣҙжөҒз”өжәҗдёҠзҡ„еҷӘеЈ°жҳҜж•°еӯ—зі»з»ҹдёӯж—¶й’ҹе’Ңж•°жҚ®жҠ–еҠЁзҡ„дё»иҰҒжқҘжәҗгҖӮеӨ„зҗҶеҷЁгҖҒеҶ…еӯҳзӯүиҠҜзүҮеҜ№зӣҙжөҒз”өжәҗзҡ„еҠЁжҖҒиҙҹиҪҪйҡҸзқҖеҗ„иҮӘж—¶й’ҹйў‘зҺҮиҖҢеҸ‘з”ҹпјҢ并еҸҜиғҪеңЁзӣҙжөҒз”өжәҗдёҠиҖҰеҗҲй«ҳйҖҹзһ¬жҖҒеҸҳеҢ–е’ҢеҷӘеЈ°пјҢе®ғ们еҢ…еҗ«дәҶ1 GHzд»ҘдёҠзҡ„йў‘зҺҮжҲҗеҲҶгҖӮ

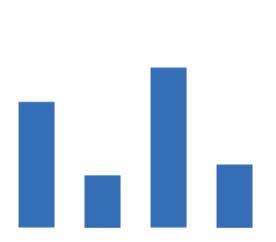

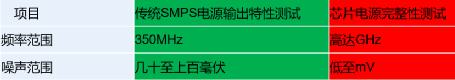

иЎЁ1 дј з»ҹз”өжәҗе’ҢиҠҜзүҮз”өжәҗйў‘зҺҮе’ҢеҷӘеЈ°иҢғеӣҙ

иЎЁ1 дј з»ҹз”өжәҗе’ҢиҠҜзүҮз”өжәҗйў‘зҺҮе’ҢеҷӘеЈ°иҢғеӣҙ 2.2 з”өжәҗеҲҶеёғзҪ‘з»ңпјҲPDNпјүеј•е…Ҙзҡ„еҷӘеЈ°е№Іжү°

2.2 з”өжәҗеҲҶеёғзҪ‘з»ңпјҲPDNпјүеј•е…Ҙзҡ„еҷӘеЈ°е№Іжү°дёәдәҶдҝқиҜҒз”өи·ҜдёҠеҗ„дёӘиҠҜзүҮзҡ„дҫӣз”өпјҢз”өжәҗеҲҶеёғзҪ‘з»ңпјҲPDNпјүйҒҚеёғж•ҙдёӘPCBгҖӮеҰӮжһңз”өжәҗеҲҶеёғзҪ‘з»ңйқ иҝ‘ж—¶й’ҹжҲ–иҖ…ж•°жҚ®зҡ„PCBиө°зәҝпјҢйӮЈд№Ҳж—¶й’ҹ/ж•°жҚ®зҡ„еҸҳеҢ–дјҡиҖҰеҗҲеҲ°з”өжәҗеҲҶеёғзҪ‘з»ңдёҠпјҢд№ҹдјҡжҲҗдёәз”өжәҗеҷӘеЈ°зҡ„жқҘжәҗгҖӮеңЁиҝҷз§Қжғ…еҶөдёӢпјҢе·ҘзЁӢеёҲиҝҳйңҖиҰҒе®ҡдҪҚз”өжәҗеҷӘеЈ°зҡ„жқҘжәҗпјҢд»ҘдҫҝеҗҺз»ӯи°ғж•ҙPCBзҡ„еёғеұҖе’ҢеёғзәҝпјҢеҮҸе°‘PDNзҪ‘з»ңеҸ—еҲ°зҡ„е№Іжү°гҖӮ

еӣҫ2 ж—¶й’ҹ/ж•°жҚ®дј иҫ“зәҝиҖҰеҗҲеҲ°з”өжәҗеҲҶеёғзҪ‘з»ңзҡ„е№Іжү°3 еҪұе“Қз”өжәҗеҷӘеЈ°жөӢиҜ•еҮҶзЎ®жҖ§зҡ„еӣ зҙ

зӨәжіўеҷЁжҳҜз”өжәҗеҷӘеЈ°жөӢиҜ•зҡ„йҮҚиҰҒд»ӘеҷЁгҖӮдёәдәҶиғҪеӨҹеҮҶзЎ®ең°жөӢйҮҸGHzеёҰе®ҪеҶ…mVзә§еҲ«зҡ„з”өжәҗеҷӘеЈ°пјҢ并е®ҡдҪҚе№Іжү°з”өжәҗеҲҶеёғзҪ‘з»ңзҡ„еҷӘеЈ°жқҘжәҗпјҢйңҖиҰҒиҖғиҷ‘еҰӮдёӢеӣ зҙ пјҡзӨәжіўеҷЁзҡ„еә•еҷӘпјҢжҺўеӨҙзҡ„иЎ°еҮҸжҜ”пјҢзӨәжіўеҷЁзҡ„еҒҸзҪ®иЎҘеҒҝиғҪеҠӣпјҢжҺўеӨҙзҡ„жҺўжҺҘж–№ејҸпјҢд»ҘеҸҠзӨәжіўеҷЁзҡ„FFTиғҪеҠӣзӯүзӯүгҖӮ

3.1 зӨәжіўеҷЁеә•еҷӘ

3.1 зӨәжіўеҷЁеә•еҷӘзӨәжіўеҷЁжң¬иә«жҳҜжңүеҷӘеЈ°зҡ„гҖӮеҪ“зӨәжіўеҷЁжөӢиҜ•з”өжәҗеҷӘеЈ°ж—¶пјҢе…¶еә•еҷӘдјҡйҷ„еҠ еҲ°иў«жөӢзҡ„з”өжәҗеҷӘеЈ°дёҠпјҢиҝӣиҖҢеҪұе“Қз”өжәҗеҷӘеЈ°зҡ„жөӢиҜ•з»“жһңгҖӮ

еӣҫ3 зӨәжіўеҷЁеә•еҷӘеҜ№з”өжәҗеҷӘеЈ°жөӢиҜ•з»“жһңзҡ„еҪұе“Қ

еӣҫ3 зӨәжіўеҷЁеә•еҷӘеҜ№з”өжәҗеҷӘеЈ°жөӢиҜ•з»“жһңзҡ„еҪұе“Қ 3.2 жҺўеӨҙзҡ„иЎ°еҮҸжҜ”

3.2 жҺўеӨҙзҡ„иЎ°еҮҸжҜ”зӣ®еүҚжңҖеёёз”Ёзҡ„500MHzеёҰе®Ҫзҡ„ж— жәҗжҺўеӨҙзҡ„иЎ°еҮҸжҜ”дёә10:1пјҢе…¶дјҡж”ҫеӨ§зӨәжіўеҷЁзҡ„еә•еҷӘпјҢеҪұе“Қз”өжәҗеҷӘеЈ°жөӢиҜ•зҡ„дёҚзЎ®е®ҡжҖ§гҖӮ

еҰӮжһңз”Ёдј з»ҹзҡ„иЎ°еҮҸжҜ”дёә1:1зҡ„ж— жәҗжҺўеӨҙпјҢеҸҜд»ҘйҒҝе…Қж”ҫеӨ§зӨәжіўеҷЁзҡ„еә•еҷӘгҖӮдҪҶжҳҜиҝҷз§ҚжҺўеӨҙзҡ„еёҰе®ҪдёҖиҲ¬еңЁ38MHzпјҢж— жі•жөӢеҲ°жӣҙй«ҳйў‘зҺҮзҡ„з”өжәҗеҷӘеЈ°гҖӮеҗҢж ·дјҡеҪұе“Қз”өжәҗеҷӘеЈ°жөӢиҜ•зҡ„дёҚзЎ®е®ҡжҖ§гҖӮ

еӣҫ4 жҺўеӨҙзҡ„иЎ°еҮҸжҜ”еҜ№з”өжәҗеҷӘеЈ°жөӢиҜ•зҡ„еҪұе“Қ

3.3 зӨәжіўеҷЁзҡ„еҒҸзҪ®иЎҘеҒҝиғҪеҠӣ

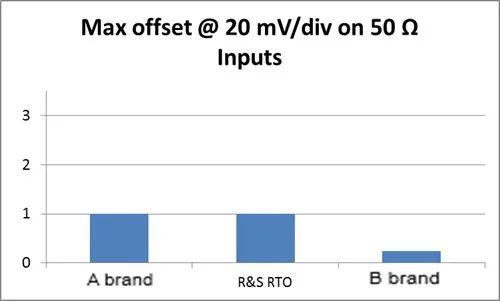

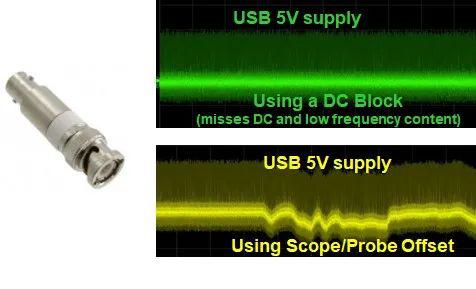

3.3 зӨәжіўеҷЁзҡ„еҒҸзҪ®иЎҘеҒҝиғҪеҠӣз”өжәҗеҷӘеЈ°жҳҜеҸ еҠ еңЁиҠҜзүҮзӣҙжөҒз”өеҺӢдёҠзҡ„еҷӘеЈ°пјҢдёәжӯӨйңҖиҰҒе°ҶзӨәжіўеҷЁзҡ„еҒҸзҪ®з”өеҺӢи®ҫеҲ°дёҺзӣҙжөҒз”өеҺӢзӣёзӯүзҡ„ж°ҙе№іпјҢеҶҚжөӢйҮҸз”өжәҗзҡ„еҷӘеЈ°гҖӮдҫӢеҰӮжҹҗиҠҜзүҮзҡ„дҫӣз”өз”өеҺӢжҳҜ3.3VпјҢйҰ–е…Ҳе°ҶзӨәжіўеҷЁзҡ„еҒҸзҪ®з”өеҺӢи°ғеҲ°3.3VпјҢ然еҗҺеҶҚжөӢиҜ•3.3VзӣҙжөҒз”өжәҗдёҠзҡ„еҷӘеЈ°жіўеҠЁпјҢдҪҶжҳҜзӨәжіўеҷЁеңЁиҜҘеҒҸзҪ®з”өеҺӢзҡ„еһӮзӣҙжҢЎдҪҚдјҡеҸ—йҷҗпјҢдёҖиҲ¬еҸӘиғҪеҲ°20mV/divпјҢз”ЁжқҘжөӢиҜ•mVзә§еҲ«зҡ„з”өжәҗеҷӘеЈ°пјҢдјҡеёҰжқҘеҫҲеӨ§зҡ„иҜҜе·®гҖӮ

еӣҫ6 йҡ”зӣҙз”өе®№еҪұе“ҚдҪҺйў‘дҝЎжҒҜ

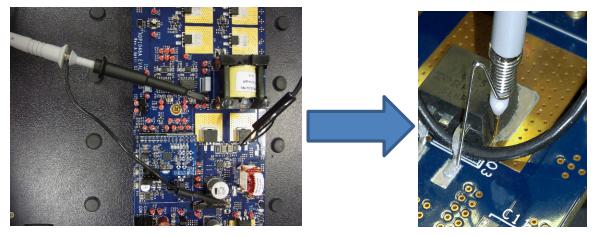

3.4 жҺўеӨҙзҡ„жҺўжҺҘж–№ејҸ

3.4 жҺўеӨҙзҡ„жҺўжҺҘж–№ејҸз”өи·ҜеҪўжҖҒеҗ„ејӮпјҢйңҖиҰҒжңүжӣҙзҒөжҙ»зҡ„ж–№жі•жқҘиҝӣиЎҢдҝЎеҸ·зҡ„жҺўжҺҘгҖӮжҺўжҺҘзҡ„зЁіе®ҡжҖ§е’ҢеҜ„з”ҹеҸӮж•°еҜ№иў«жөӢз”өжәҗз”өи·Ҝзҡ„еҪұе“ҚдёҚеҸҜеҝҪи§ҶпјҢжүҖд»ҘйңҖиҰҒе°ҪйҮҸиҙҙиҝ‘иҠҜзүҮзҡ„з®Ўи„ҡпјҢ并дҪҝз”Ёзҹӯең°зәҝгҖӮ

еӣҫ7 иҙҙиҝ‘иҠҜзүҮз®Ўи„ҡпјҢдҪҝз”Ёзҹӯең°зәҝ

еӣҫ7 иҙҙиҝ‘иҠҜзүҮз®Ўи„ҡпјҢдҪҝз”Ёзҹӯең°зәҝ 3.5 зӨәжіўеҷЁзҡ„FFTиғҪеҠӣ

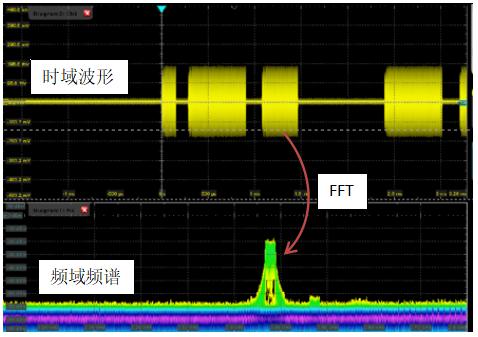

3.5 зӨәжіўеҷЁзҡ„FFTиғҪеҠӣз”ұдәҺз”өжәҗеҲҶеёғзҪ‘з»ңPDNдјҡеҸ—еҲ°е№Іжү°еҷӘеЈ°зҡ„жқҘжәҗпјҢеӣ жӯӨйңҖиҰҒзӨәжіўеҷЁе…·жңүејәеӨ§зҡ„FFTеҲҶжһҗиғҪеҠӣпјҢд»ҘдҫҝеҲҶжһҗзҡ„е№Іжү°еҷӘеЈ°зҡ„йў‘зҺҮпјҢиҝӣиҖҢжҺ’жҹҘеҷӘеЈ°зҡ„жәҗеӨҙгҖӮ

еӣҫ8 FFTеҲҶжһҗз”өжәҗеҷӘеЈ°зҡ„йў‘и°ұеЈ°жҳҺпјҡжң¬ж–ҮиҪ¬иҮӘзҪ‘з»ңпјҢзүҲжқғеҪ’еҺҹдҪңиҖ…жүҖжңүгҖӮеҰӮжңүдҫөжқғпјҢиҜ·иҒ”зі»жҲ‘们еҲ йҷӨпјҒ

еӣҫ8 FFTеҲҶжһҗз”өжәҗеҷӘеЈ°зҡ„йў‘и°ұеЈ°жҳҺпјҡжң¬ж–ҮиҪ¬иҮӘзҪ‘з»ңпјҢзүҲжқғеҪ’еҺҹдҪңиҖ…жүҖжңүгҖӮеҰӮжңүдҫөжқғпјҢиҜ·иҒ”зі»жҲ‘们еҲ йҷӨпјҒ????зӮ№еҮ»е…іжіЁпјҢжҠҖжңҜе№Іиҙ§еҮҶж—¶йҖҒиҫҫпјҒ????