еүҚйқўдёҖзҜҮж–Үз« жҖ»з»“дәҶдёҖдёӢе·ҘдёҡHARTжҖ»зәҝпјҢд»ҠеӨ©жқҘиҒҠиҒҠRS-485жҖ»зәҝгҖӮRS-485д№ҹжҳҜеә”з”Ёйқһеёёе№ҝжіӣзҡ„дёҖз§ҚйҖҡдҝЎжҺҘеҸЈпјҢжң¬ж–ҮжқҘи®Ёи®әдёҖдёӢиҰҒзӮ№пјҢж–Үз« зЁҚеҫ®жңүзӮ№й•ҝпјҢзәҰ5000еӯ—гҖӮ

еүҚдё–д»Ҡз”ҹ

RS-485пјҢRSжҳҜд»Җд№Ҳж„ҸжҖқе‘ўпјҹжҳҜRecommended Standardзҡ„зј©еҶҷпјҢе°ұжҳҜжҺЁиҚҗж ҮеҮҶзҡ„ж„ҸжҖқгҖӮ485жҳҜж ҮеҮҶж ҮиҜҶеҸ·пјҢиҮідәҺдёәд»Җд№Ҳе®ҡиҝҷдёӘж ҮиҜҶеҸ·пјҢеҲҷж— йңҖж·ұ究гҖӮRS-485еҸҲз§°дёәANSI/TIA/EIA-485пјҢиҝҷеҮ дёӘеүҚзјҖжҳҜж ҮеҮҶеҚҸдјҡзҡ„еҗҚз§°зј©еҶҷпјҢжҜ”еҰӮEIAе°ұжҳҜз”өеӯҗе·ҘдёҡеҚҸдјҡ (Electronics Industries Association EIA)зҡ„зј©еҶҷгҖӮ1983е№ҙпјҢRS-485йҖҡи®ҜжҺҘеҸЈиў«з”өеӯҗе·ҘдёҡеҚҸдјҡ (Electronics Industries Association EIA)жү№еҮҶдёәдёҖз§ҚйҖҡи®ҜжҺҘеҸЈж ҮеҮҶгҖӮеҚідҫҝеңЁзҺ°еңЁIOTзҒ«зғӯзҡ„д»ҠеӨ©пјҢRS-485д»Қ然жңүеӨ§йҮҸзҡ„еә”з”ЁгҖӮеҫҲеӨҡеҚҸи®®дҪҝз”ЁRS-485дҪңдёәзү©зҗҶеұӮпјҢжҜ”еҰӮеёёз”Ёж ҮеҮҶеҚҸи®®дҪҝз”ЁRS-485дҪңдёәзү©зҗҶеұӮзҡ„жңүе“Әдәӣе‘ўпјҹжҜ”еҰӮпјҡ- е·ҘдёҡHARTжҖ»зәҝ

- modbusеҚҸи®®

- Profibus DP

- .......

з”өж°”зү№жҖ§

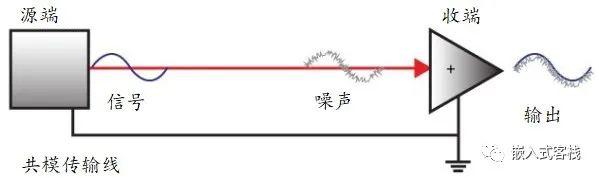

дҝЎеҸ·йҮҮж ·е·®жЁЎдј иҫ“пјҢе·®жЁЎжҳҜзӣёеҜ№дәҺе…ұжЁЎиҖҢиЁҖзҡ„пјҢе·®жЁЎд№ҹз§°дёәе·®еҲҶпјҢйӮЈд№Ҳд»Җд№Ҳж ·зҡ„дј иҫ“жҳҜе·®жЁЎе‘ўпјҹдёҖеӣҫиғңеҚғиЁҖпјҢзңӢдёӢйқўдёӨдёӘеӣҫе°ұжҳҺзҷҪдәҶпјҡе…ұжЁЎдј иҫ“

е·®жЁЎдј иҫ“

еҜ№дәҺиҝҷдёӘе№Іжү°пјҢжҲ‘们жқҘе®һйҷ…жҠ“дёӘжіўеҪўзңӢзңӢпјҡ

еңЁA/BдҝЎеҸ·зҡ„иҫ№зјҳеӨ„пјҢжіўеҪўйғҪз•Ҙеҫ®жңүдәӣеҸҳеҪўпјҢдҪҶжҳҜдҪ зңӢA-BеҒҡе·®пјҲзәўиүІзҡ„дёәзӨәжіўеҷЁзҡ„MATHеҮҸеҠҹиғҪпјҢдёәA-BпјүпјҢиҫ№жІҝеҲҷеҸҳеҫ—йқһеёёзҡ„е№ІеҮҖпјҒиҝҷдҫӢеӯҗе°ұеҸҜд»ҘеҫҲеҘҪең°иҜҙжҳҺе·®жЁЎдј иҫ“еҸҜд»Ҙжңүж•Ҳзҡ„жҠөжҠ—е…ұжЁЎе№Іжү°гҖӮ

еңЁA/BдҝЎеҸ·зҡ„иҫ№зјҳеӨ„пјҢжіўеҪўйғҪз•Ҙеҫ®жңүдәӣеҸҳеҪўпјҢдҪҶжҳҜдҪ зңӢA-BеҒҡе·®пјҲзәўиүІзҡ„дёәзӨәжіўеҷЁзҡ„MATHеҮҸеҠҹиғҪпјҢдёәA-BпјүпјҢиҫ№жІҝеҲҷеҸҳеҫ—йқһеёёзҡ„е№ІеҮҖпјҒиҝҷдҫӢеӯҗе°ұеҸҜд»ҘеҫҲеҘҪең°иҜҙжҳҺе·®жЁЎдј иҫ“еҸҜд»Ҙжңүж•Ҳзҡ„жҠөжҠ—е…ұжЁЎе№Іжү°гҖӮз”өж°”еҸӮж•°

RS-485зҡ„з”өж°”еҸӮж•°дёәпјҡ- е…ұжЁЎз”өеҺӢиҢғеӣҙдёә-7пҪһ+12V

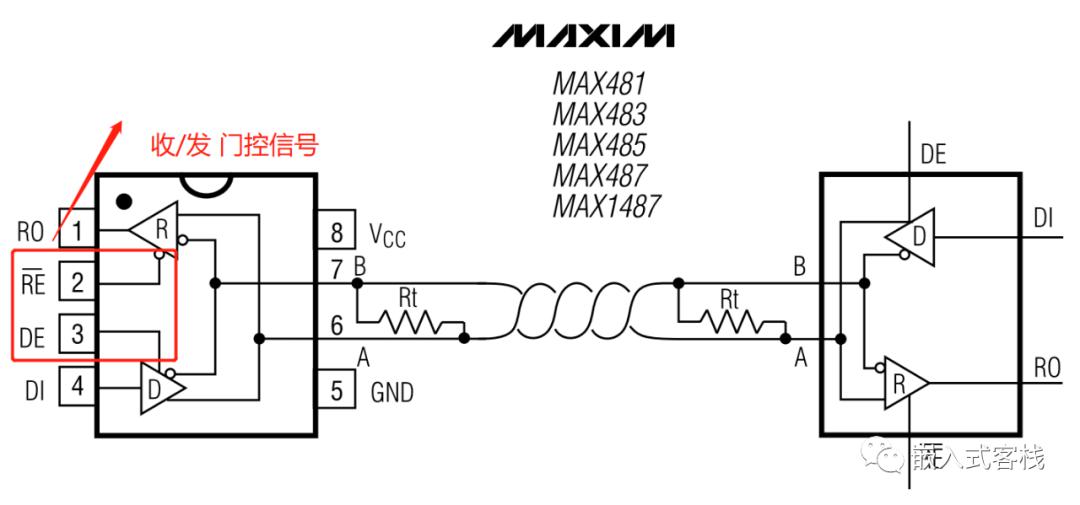

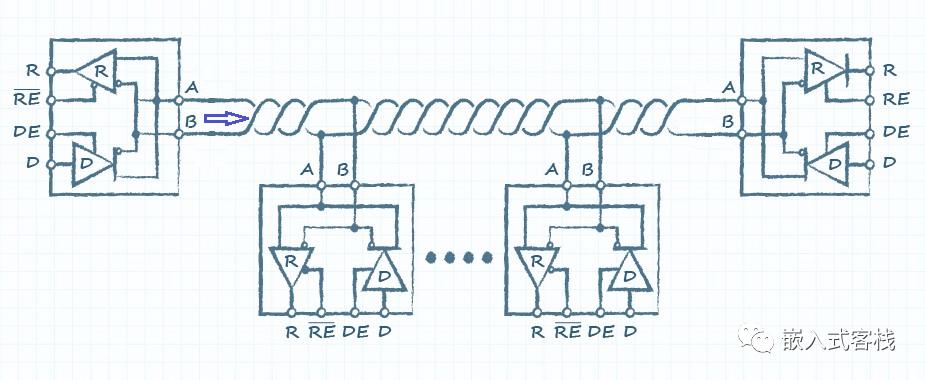

- еҸҜж”ҜжҢҒ32дёӘеӨҡзӮ№жӢ“жү‘иҝһжҺҘпјҢи§ҒдёӢйқўзҡ„зҪ‘з»ңжӢ“жү‘еӣҫ

- дҪҝз”Ё40иӢұе°әзәҝзјҶж—¶пјҢдј иҫ“йҖҹзҺҮеҸҜиҫҫ10MbpsпјҢ1иӢұе°әзӣёеҪ“дәҺ30.48cmпјҢиҝҷйҮҢMbpsжҳҜе…Ҷbit/sзҡ„ж„ҸжҖқ

- дҪҝз”Ё4000иӢұе°әзәҝзјҶж—¶пјҢдј иҫ“йҖҹзҺҮеҸҜиҫҫеҲ°100kbps

- еҚҠеҸҢе·ҘйҖҡдҝЎ

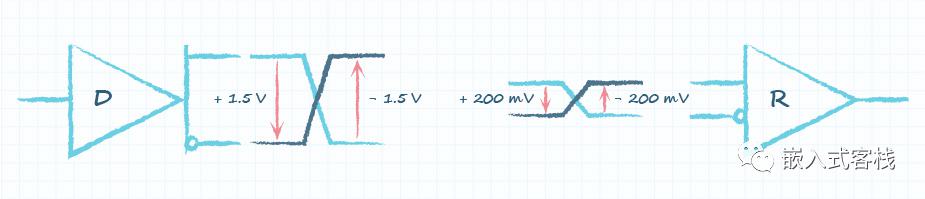

- жңҖе°Ҹе·®еҲҶз”өеҺӢе®№йҷҗпјҡ200mV,д№ҹе°ұжҳҜиҜҙжҺҘ收з«ҜеңЁе·®еҲҶз”өеҺӢдҪҺдәҺ200mVж—¶е°ұж— жі•жӯЈзЎ®иҜҶеҲ«0/1дәҶгҖӮиҝҷеҸҘиҜқеә”иҜҘжҖҺд№ҲзҗҶи§Је‘ўпјҹ

дёҠйқўиҝҷдёӘеӣҫжҖҺд№ҲзҗҶи§Је‘ўпјҹRS-485收еҸ‘еҷЁзҡ„еҸ‘йҖҒз”өи·ҜиҮіе°‘жҸҗдҫӣ1.5Vе·®еҲҶз”өеҺӢиҫ“еҮәиғҪеҠӣпјҢз»Ҹз”ұжҖ»зәҝзәҝи·Ҝйҳ»жҠ—иЎ°еҮҸпјҢ32дёӘжҺҘ收з”өи·Ҝиҫ“е…Ҙйҳ»жҠ—пјҢд»ҘеҸҠ120в„Ұз«ҜжҺҘз”өйҳ»пјҢе·®еҲҶдҝЎеҸ·зҡ„е№…еәҰеҝ…然йҖҗжёҗиЎ°еҮҸпјҢйӮЈд№ҲиҮіжңҖжң«з«ҜиҝҳйңҖиҰҒиҮіе°‘жҸҗдҫӣ200mVзҡ„е·®еҲҶз”өеҺӢз»ҷжң«з«ҜжҺҘ收з”өи·ҜгҖӮ

пјҡеҜ№дәҺжҺҘ收з”өи·ҜжҳҜеҲӨеҶіAзәҝе…ұжЁЎз”өеҺӢдёҺBзәҝе…ұжЁЎз”өеҺӢд№Ӣе·®пјҡ

- еҰӮжһң ,еҲҷжҺҘ收з”өи·ҜRиҜҶеҲ«дёәйҖ»иҫ‘ 1

- еҰӮжһң ,еҲҷжҺҘ收з”өи·ҜRиҜҶеҲ«дёәйҖ»иҫ‘0

д»Һиҝҷж ·дёҖдёӘжҺҘеҸЈз”өи·ҜжқҘзңӢпјҢжңүиҝҷд№ҲдәӣиҰҒзӮ№пјҡ

д»Һиҝҷж ·дёҖдёӘжҺҘеҸЈз”өи·ҜжқҘзңӢпјҢжңүиҝҷд№ҲдәӣиҰҒзӮ№пјҡ- RS-485йҖҡдҝЎд»ҺеҚ•зүҮжңә/DSP/еӨ„зҗҶеҷЁжҺҘеҸЈиҖҢиЁҖпјҢжҳҜеҲ©з”ЁUARTжҺҘеҸЈдёҺRS-485收еҸ‘еҷЁжҺҘеҸЈгҖӮеҪ“然дҪ иҜҙжҲ‘з”ЁFPGAйҡҫйҒ“дёҚиЎҢд№ҲпјҹиӮҜе®ҡжҳҜеҸҜд»Ҙзҡ„пјҢз”ЁFPGAе®һзҺ°дёҖдёӘдёІеҸЈж”¶еҸ‘зҡ„IPжЁЎеқ—пјҢеҪ“然д№ҹжҳҜеҸҜд»Ҙзҡ„гҖӮз”ҡиҮідҪ жғіиҜҙпјҢжҲ‘жӢҝGPIOеҺ»жЁЎжӢҹдёҖдёӢ UART жҳҜдёҚжҳҜе°ұдёҚиЎҢпјҹд№ҹжҳҜиғҪеҠһеҫ—еҲ°зҡ„пјҢеҸӘдёҚиҝҮиҝҷд№Ҳе№Іж„Ҹд№үдёҚеӨ§пјҢйңҖиҰҒеҚ з”ЁCPUиө„жәҗе®һзҺ°еә•еұӮBITзҡ„收еҸ‘гҖӮ

- еүҚйқўиҜҙеҲ°еҚҠеҸҢе·ҘпјҢжңүеҚҠеҸҢе·Ҙе°ұжңүе…ЁеҸҢе·ҘгҖӮд»Җд№ҲжҳҜеҚҠеҸҢе·Ҙе‘ўпјҹйҰ–е…ҲеҚҠеҸҢе·Ҙд»ҘеҸҠе…ЁеҸҢе·ҘпјҢжүҖз•Ңе®ҡзҡ„еҜ№иұЎдёҖе®ҡжҳҜзӮ№еҜ№зӮ№иҖҢиЁҖзҡ„пјҢиҝҷйҮҢиҜҙзӮ№еҜ№зӮ№е°ұжҳҜжҢҮеңЁеҗҢдёҖж—¶еҲ»иҖҢиЁҖпјҢжүҖи°“еҚҠеҸҢе·ҘпјҢе°ұжҳҜи®ҫеӨҮеңЁеҗҢдёҖж—¶еҲ»иҰҒд№ҲеӨ„дәҺ收数жҚ®зҠ¶жҖҒпјҢ иҰҒд№ҲеӨ„дәҺеҸ‘ж•°жҚ®зҠ¶жҖҒпјҢ дёҚе…Ғи®ёеҗҢ时收еҸ‘ж•°жҚ®гҖӮ е…ЁеҸҢе·ҘеҲҷеҲҡеҘҪзӣёеҸҚпјҢе…Ғи®ёеҗҢ时收еҸ‘гҖӮжҜ”еҰӮ I2C жҖ»зәҝе°ұжҳҜеҚҠеҸҢе·ҘжҖ»зәҝпјҢ4зәҝеҲ¶ SPI жҳҜе…ЁеҸҢе·ҘпјҢиҖҢдёүзәҝеҲ¶SPIеҲҷжҳҜеҚҠеҸҢе·ҘжҖ»зәҝпјӣеҸҲиӯ¬еҰӮRS-422жҲ–иҖ…RS-232 жҳҜе…ЁеҸҢе·ҘжҺҘеҸЈпјӣиҖҢCANжҖ»зәҝеҲҷжҳҜеҚҠеҸҢе·ҘжҖ»зәҝгҖӮRS-485е°ұжҳҜдёҖз§ҚеҚҠеҸҢе·ҘжҖ»зәҝпјҡ

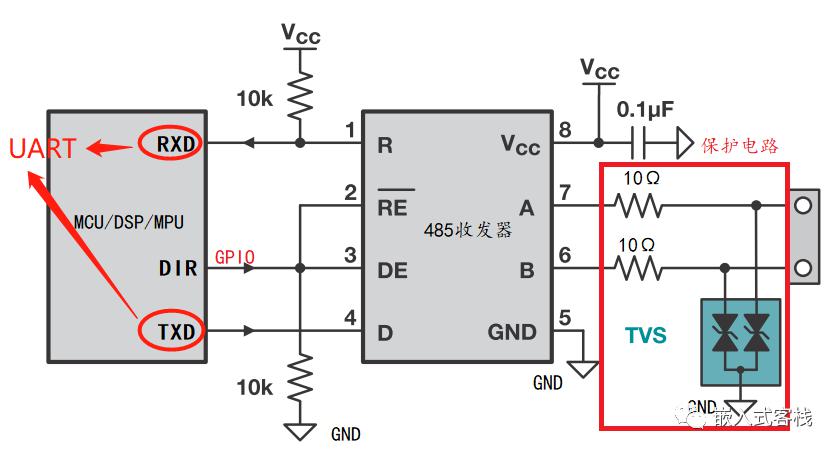

- еҪ“HostеҸ‘йҖҒж•°жҚ®ж—¶пјҢж•°жҚ®жІҝзқҖзәўиүІзҡ„зәҝз»Ҹз”ұеҸҢз»һзәҝпјҢдј иҫ“иҮіSlaveзҡ„е·®еҲҶжҺҘ收з”өи·ҜпјҢеҪ“slaveеә”зӯ”ж—¶пјҢж•°жҚ®жІҝзқҖе…°иүІзҡ„ж–№еҗ‘дј иҫ“иҮіHostзҡ„жҺҘ收з”өи·ҜпјҢдҪҶжҳҜдј иҫ“д»ӢиҙЁжҳҜдёҖеҜ№еҸҢз»һзәҝпјҢжүҖд»ҘдёҖж–№еңЁдј иҫ“ж•°жҚ®зҡ„ж—¶еҖҷпјҢеҸҰдёҖж–№жҳҜж— жі•дј иҫ“дҝЎеҸ·зҡ„пјҢд»Һ收еҸ‘еҷЁзҡ„жҺ§еҲ¶и§’еәҰжқҘзңӢпјҡжҺ§еҲ¶иҠҜзүҮдҫ§пјҢз”ЁдёҖдёӘGPIOи„ҡжқҘжҺ§еҲ¶ж”¶еҸ‘дҪҝиғҪпјҢжқҘдёҖеј иҠҜзүҮеҶ…йғЁеҺҹзҗҶжЎҶеӣҫпјҢе°ұеҫҲе®№жҳ“зҗҶи§ЈдәҶпјҡ

- еҪ“DIR=0ж—¶пјҢжҺҘ收з”өи·ҜдҪҝиғҪпјҢеҸ‘йҖҒз”өи·ҜзҰҒжӯўDE=0пјҢеҜ№жҖ»зәҝиҖҢиЁҖзӣёеҪ“дәҺй«ҳйҳ»пјӣеҪ“ DIR=1 ж—¶пјҢжҺҘ收з”өи·ҜдҪҝиғҪ пјҢеҸ‘йҖҒз”өи·ҜзҰҒжӯўDE=1пјҢеҜ№жҖ»зәҝA/BдҝЎеҸ·еҸ–еҶідәҺDIзҡ„дҝЎеҸ·гҖӮиҝҷйҮҢжңүдёӨдёӘй—®йўҳпјҡ1.дёәд»Җд№ҲиҠҜзүҮиҰҒжҠҠе’Ңи®ҫи®ЎжҲҗзӣёеҸҚзҡ„жңүж•ҲйҖ»иҫ‘е‘ўпјҹиҝҷж ·е…¶е®һд№ҹжҳҜж–№дҫҝз”ЁдёҖдёӘGPIOеҗҢж—¶жҺ§еҲ¶ж”¶еҸ‘з”өи·Ҝзҡ„иҖғиҷ‘гҖӮ2.йӮЈж”¶еҸ‘еҷЁиҠҜзүҮ收еҸ‘дҪҝиғҪдёәд»Җд№ҲдёҚеҒҡжҲҗдёҖдёӘи„ҡе‘ўпјҹжҜ”еҰӮе°ұеҸ«DIRпјҹеҒҡжҲҗдёӨдёӘи„ҡ收/еҸ‘д№ҹеҸҜд»Ҙз”ЁдёӨдёӘи„ҡеҚ•зӢ¬жҺ§еҲ¶пјҢжҜ”еҰӮпјҡ

- з”ҡиҮіеҸҜд»ҘеңЁDE=1зҡ„ж—¶еҖҷпјҢе°Ҷи®ҫзҪ®дёә0пјҢиҝҷж ·жҳҜдёҚжҳҜе°ұеҸҜд»ҘиҮӘзҺҜдәҶпјҹдә§е“Ғдёӯд№ҹеҸҜд»Ҙе°ұиҝҷж ·и®ҫи®ЎпјҢеҸҜд»Ҙе®һзҺ°ж”¶еҸ‘еҷЁд»ҘеҸҠеёғзәҝзҡ„иҮӘиҜҠж–ӯпјҢйҖҡиҝҮжҺҘ收еҲ°зҡ„жҠҘж–ҮдёҺеҸ‘йҖҒеҮәеҺ»зҡ„жҠҘж–ҮжҜ”иҫғпјҢеҸҜд»ҘиҜҠж–ӯеҮәиҠҜзүҮз„ҠжҺҘпјҢ收еҸ‘еҷЁжҳҜеҗҰжҚҹеқҸжҲ–иҖ…ж–ӯи·ҜпјҢд»ҘеҸҠеёғзәҝжҳҜеҗҰеӯҳеңЁзҹӯи·Ҝж•…йҡңгҖӮжҲ–и®ёдҪ дјҡиҜҙпјҢзһҺжүҜпјҒдҪ еүҚйқўжүҚиҜҙRS-485дёҚиғҪеҗҢ时收еҸ‘пјҢиҝҷйҮҢеҸҲиҜҙиғҪеҗҢ时收еҸ‘пјҢеІӮдёҚжҳҜиҮӘзӣёзҹӣзӣҫеҗ—пјҹдёҚзҹӣзӣҫпјҢеүҚйқўжүҖиҜҙзҡ„дёҚиғҪеҗҢ时收еҸ‘пјҢжҳҜжҢҮеҸ‘зҡ„еҗҢж—¶дёҚиғҪ收жқҘиҮӘе…¶д»–и®ҫеӨҮзҡ„еҸ‘йҖҒжҠҘж–ҮпјҢиҝҷйҮҢ收зҡ„жҳҜиҮӘиә«еҸ‘еҮәзҡ„жҠҘж–ҮгҖӮжүҖд»ҘеҚҠеҸҢе·Ҙзҡ„жң¬иҙЁпјҢжҳҜйҖҡи®Ҝд»ӢиҙЁдёҚеӯҳеңЁеҸҢеҗ‘йҖҡйҒ“пјҢеңЁеҗ‘жҖ»зәҝеҸ‘йҖҒж•°жҚ®зҡ„ж—¶еҖҷпјҢд»ӢиҙЁиў«еҚ з”ЁпјҢеҚідҫҝжғіеҸ‘йҖҒд№ҹжҳҜж— жі•жӯЈзЎ®зҡ„е°ҶдҝЎеҸ·еҸ‘йҖҒеҲ°д»ӢиҙЁдёҠзҡ„пјҢеҰӮжһңејәиЎҢеҸ‘йҖҒпјҢж•°жҚ®е°Ҷдјҡй”ҷд№ұпјҢз”ҡиҮіж”¶еҸ‘еҷЁиҠҜзүҮжңүеҸҜиғҪжҚҹеқҸгҖӮ

- : Receiver Output Enable,жҺҘ收еҷЁдҪҝиғҪпјҢ

- DEпјҡDriver Output EnableпјҢй©ұеҠЁиҫ“еҮәдҪҝиғҪ

- еӣҫдёӯзҡ„DIRи„ҡе°ұжҳҜжҺ§еҲ¶еҪ“еүҚRS-485жҳҜеӨ„дәҺвҖң收вҖқиҝҳжҳҜеӨ„дәҺвҖңеҸ‘вҖқжЁЎејҸгҖӮ

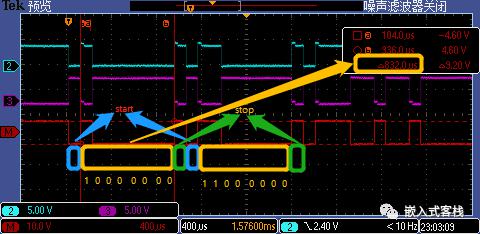

зӨәжіўеҷЁзҡ„CH2жҺҘ485иҫ“еҮәAз«ҜпјҢCH3жҺҘ485иҫ“еҮәAз«ҜпјҢзәўиүІзҡ„дёәзӨәжіўеҷЁзҡ„MATHеҠҹиғҪпјҡCH2-CH3гҖӮеӨ§йғЁеҲҶзӨәжіўеҷЁйғҪе…·жңүж•°еӯҰиҝҗз®—еҠҹиғҪгҖӮ

зӨәжіўеҷЁзҡ„CH2жҺҘ485иҫ“еҮәAз«ҜпјҢCH3жҺҘ485иҫ“еҮәAз«ҜпјҢзәўиүІзҡ„дёәзӨәжіўеҷЁзҡ„MATHеҠҹиғҪпјҡCH2-CH3гҖӮеӨ§йғЁеҲҶзӨәжіўеҷЁйғҪе…·жңүж•°еӯҰиҝҗз®—еҠҹиғҪгҖӮеҰӮжһңжғізңӢе·®еҲҶдҝЎеҸ·пјҢе°ұеҸҜд»ҘеҲ©з”ЁеҸҢйҖҡйҒ“зӨәжіўеҷЁеҠ MATHеҮҸеҠҹиғҪи§ӮжөӢгҖӮжҲ–и®ёжңүзҡ„зӨәжіўеҷЁжІЎжңүMATHеҠҹиғҪпјҢйӮЈд№ҲиҝҷйҮҢиҝҳеҸҜд»ҘдҪҝз”ЁдёҖдёӘжҠҖе·§пјҡ

е°ҶBйҖҡйҒ“пјҢжҲ–иҖ…иҜҙе·®еҲҶдҝЎеҸ·зҡ„иҙҹз«ҜеҸҚзӣёпјҢ然еҗҺе°ҶBйҖҡйҒ“дёҠ移иҮіз©әй—Із”өе№ійҮҚеҗҲпјҢиҝҷж ·жҳҜдёҚжҳҜд№ҹе°ұжҜ”иҫғзӣҙи§Ӯзҡ„еҸҜд»ҘзңӢеҮәA-BдәҶпјҹйҖҡиҝҮиҝҷдёӘеӣҫпјҢиғҪеҸ‘зҺ°е“Әдәӣжңүд»·еҖјзҡ„дҝЎеҸ·зү№еҫҒе‘ўпјҹ

е°ҶBйҖҡйҒ“пјҢжҲ–иҖ…иҜҙе·®еҲҶдҝЎеҸ·зҡ„иҙҹз«ҜеҸҚзӣёпјҢ然еҗҺе°ҶBйҖҡйҒ“дёҠ移иҮіз©әй—Із”өе№ійҮҚеҗҲпјҢиҝҷж ·жҳҜдёҚжҳҜд№ҹе°ұжҜ”иҫғзӣҙи§Ӯзҡ„еҸҜд»ҘзңӢеҮәA-BдәҶпјҹйҖҡиҝҮиҝҷдёӘеӣҫпјҢиғҪеҸ‘зҺ°е“Әдәӣжңүд»·еҖјзҡ„дҝЎеҸ·зү№еҫҒе‘ўпјҹ- дҝЎеҸ·AеңЁз©әй—Іж—¶еҖҷдёәй«ҳз”өе№іпјӣдҝЎеҸ·BеңЁз©әй—Іж—¶дёәдҪҺз”өе№ігҖӮжүҖд»ҘдҪ дјҡзңӢеҲ°жңүи®ҫеӨҮдёҠдјҡж ҮиҜҶ485_A+пјҢ485_B-гҖӮ

- жҜҸдёӘйҖҡйҒ“зҡ„е…ұжЁЎз”өеҺӢеҖјйғҪеңЁж ҮеҮҶиҰҒжұӮзҡ„-7пҪһ12Vд№ӢеҶ…пјҢдҝЎеҸ·Aдёә4VпјҢдҝЎеҸ·Bдёә5Vпјҡ

йӮЈд№Ҳж•°жҚ®жҖҺд№ҲеҺ»и§ЈиҜ»е‘ўпјҹ

йӮЈд№Ҳж•°жҚ®жҖҺд№ҲеҺ»и§ЈиҜ»е‘ўпјҹиҝҷйҮҢжҠ“зҡ„ж•°жҚ®жҳҜдёҖдёӘMODBUS-RTUдё»з«ҜеҸ‘йҖҒз»ҷд»Һи®ҫеӨҮзҡ„жҠҘж–ҮпјҢе…¶еҶ…е®№еүҚйқўдёӨдёӘеӯ—иҠӮжҳҜ0x01 0x03пјҢUARTжЁЎејҸдёә1дёӘиө·е§ӢдҪҚпјҢ8дёӘж•°жҚ®дҪҚпјҢ1дёӘеҒңжӯўдҪҚпјҢж— ж ЎйӘҢдҪҚпјҢдҪҺдҪҚеңЁеүҚпјҢжӯӨдҫӢдёӯUARTзҡ„йҖҡи®Ҝж јејҸдёә

е…Ҳж №жҚ®UARTйҖҡи®ҜжЁЎејҸпјҢжқҘи®Ўз®—дёҖдёӢеҮ дёӘеҸӮж•°пјҢжҜҸbitеҚ з”Ёж—¶й—ҙпјҢжҜҸеӯ—иҠӮеҚ з”Ёж—¶й—ҙпјҡ

е…Ҳж №жҚ®UARTйҖҡи®ҜжЁЎејҸпјҢжқҘи®Ўз®—дёҖдёӢеҮ дёӘеҸӮж•°пјҢжҜҸbitеҚ з”Ёж—¶й—ҙпјҢжҜҸеӯ—иҠӮеҚ з”Ёж—¶й—ҙпјҡ иҝҷдёӘеӣҫе°ұжҳҜиө·е§ӢдҪҚпјҢе®ҪеәҰжӯЈеҘҪжҳҜ104usгҖӮ

иҝҷдёӘеӣҫе°ұжҳҜиө·е§ӢдҪҚпјҢе®ҪеәҰжӯЈеҘҪжҳҜ104usгҖӮеҜ№дәҺи§Јжһҗиҝҷз§ҚејӮжӯҘдёІиЎҢж—¶еәҸжіўеҪўиҖҢиЁҖпјҢжңҖйҮҚиҰҒе°ұжҳҜж №жҚ®йҖҡдҝЎж јејҸи®Ўз®—дҪҚж—¶й—ҙпјҢеӯ—иҠӮж—¶й—ҙпјҢиҝӣиҖҢеҸҜд»ҘзӣҙжҺҘи§ЈжһҗжіўеҪўж•°жҚ®гҖӮд»ҺиҝҷдёҖзӮ№жҖқиҖғпјҢеҒҮи®ҫиҰҒеҲ©з”ЁFPGAжқҘе®һзҺ°дёҖдёӘUARTеҚҸи®®йҖ»иҫ‘еҲҶжһҗд»ӘпјҢиҝҷе°ұжҳҜжңҖдёәж ёеҝғзҡ„жҢҮж ҮпјҢйҖҡиҝҮжЈҖжөӢеҲ°иө·е§ӢдҪҚиҫ№жІҝпјҢиҝӣиҖҢйҖҡиҝҮж—¶й—ҙиҪҙе°Ҷж•°жҚ®и§ЈжһҗеҮәжқҘгҖӮиҝҷйҮҢжҲ‘жқҘе……еҪ“дёҖдёӘиӮүзңјUARTйҖ»иҫ‘еҲҶжһҗд»Әеҗ§пјҡ

8bitж•°жҚ®зҡ„ж—¶й—ҙе®ҪеәҰеҲҡеҘҪжҳҜ832usпјҢз”ұдәҺж јејҸжҳҜдҪҺдҪҚеңЁеүҚпјҢжүҖд»ҘиҰҒеҸҚиҝҮжқҘзңӢпјҢдёҺе®һйҷ…еҸ‘йҖҒзҡ„ж•°жҚ®0x01 0x03жҳҜеҗ»еҗҲзҡ„гҖӮиҝҷйҮҢеңЁи°ғиҜ•еә•еұӮзҡ„ж—¶еҖҷйҒҮеҲ°й—®йўҳпјҢе°ұеҸҜд»ҘйҖҡиҝҮиҝҷз§Қж–№ејҸеҸҜд»ҘжЈҖжҹҘиҪҜ件жҳҜеҗҰжӯЈзЎ®зҡ„й©ұеҠЁдәҶ硬件пјҢиӯ¬еҰӮеңЁи°ғиҜ•I2C/SPIзӯүзӯүе…¶д»–еә•еұӮжҺҘеҸЈзҡ„ж—¶еҖҷпјҢйғҪеҸҜд»Ҙзұ»дјјзҡ„еҺ»жЈҖжҹҘ硬件波еҪўпјҢе”ҜдёҖдёҚдёҖж ·зҡ„жҳҜпјҢI2C/SPIеұһдәҺеҗҢжӯҘйҖҡдҝЎпјҢжүҖи°“еҗҢжӯҘйҖҡдҝЎпјҢжҳҜжҢҮе…¶йҖҡдҝЎеә•еұӮжңүеҗҢжӯҘж—¶й’ҹдҝЎеҸ·пјҢI2Cзҡ„SCL,SPIзҡ„SCKйғҪеұһдәҺеҗҢжӯҘж—¶й’ҹгҖӮ

8bitж•°жҚ®зҡ„ж—¶й—ҙе®ҪеәҰеҲҡеҘҪжҳҜ832usпјҢз”ұдәҺж јејҸжҳҜдҪҺдҪҚеңЁеүҚпјҢжүҖд»ҘиҰҒеҸҚиҝҮжқҘзңӢпјҢдёҺе®һйҷ…еҸ‘йҖҒзҡ„ж•°жҚ®0x01 0x03жҳҜеҗ»еҗҲзҡ„гҖӮиҝҷйҮҢеңЁи°ғиҜ•еә•еұӮзҡ„ж—¶еҖҷйҒҮеҲ°й—®йўҳпјҢе°ұеҸҜд»ҘйҖҡиҝҮиҝҷз§Қж–№ејҸеҸҜд»ҘжЈҖжҹҘиҪҜ件жҳҜеҗҰжӯЈзЎ®зҡ„й©ұеҠЁдәҶ硬件пјҢиӯ¬еҰӮеңЁи°ғиҜ•I2C/SPIзӯүзӯүе…¶д»–еә•еұӮжҺҘеҸЈзҡ„ж—¶еҖҷпјҢйғҪеҸҜд»Ҙзұ»дјјзҡ„еҺ»жЈҖжҹҘ硬件波еҪўпјҢе”ҜдёҖдёҚдёҖж ·зҡ„жҳҜпјҢI2C/SPIеұһдәҺеҗҢжӯҘйҖҡдҝЎпјҢжүҖи°“еҗҢжӯҘйҖҡдҝЎпјҢжҳҜжҢҮе…¶йҖҡдҝЎеә•еұӮжңүеҗҢжӯҘж—¶й’ҹдҝЎеҸ·пјҢI2Cзҡ„SCL,SPIзҡ„SCKйғҪеұһдәҺеҗҢжӯҘж—¶й’ҹгҖӮй©ұеҠЁиғҪеҠӣ

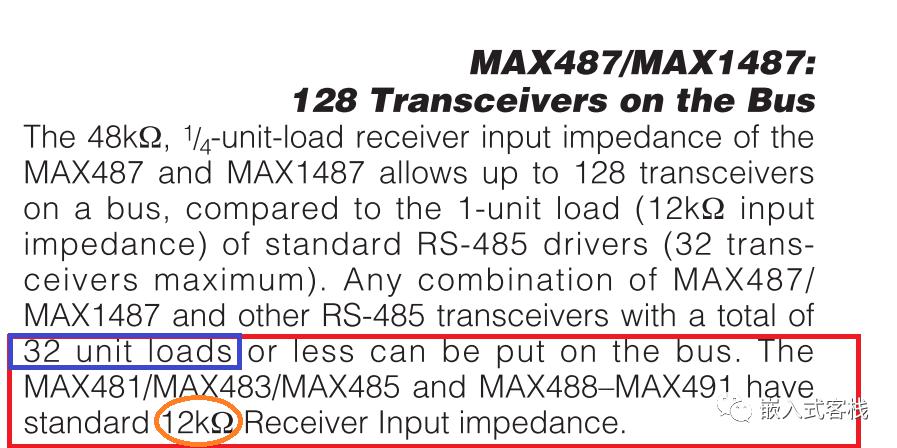

з”өж°”еҸӮж•°йҮҢжҖ»з»“иҜҙRS-485жңҖеӨ§з”өж°”й©ұеҠЁиғҪеҠӣпјҢеңЁеӨҡзӮ№зҪ‘з»ңжӢ“жү‘з»“жһ„дёӢпјҢеҸҜжңҖеӨ§й©ұеҠЁ32дёӘз«ҷзӮ№гҖӮйӮЈд№ҲжҖҺд№ҲеҺ»и§ЈиҜ»иҝҷдёҖжҢҮж Үе‘ўпјҹйҰ–е…ҲжқҘиҖғеҜҹдёҖдёӘз«ҷзӮ№ж”¶еҸ‘з”өи·Ҝзү№жҖ§пјҢ收еҸ‘еҷЁзҡ„жҺҘ收з”өи·Ҝе…¶ж ҮеҮҶзӯүж•Ҳиҫ“е…Ҙйҳ»жҠ—дёә12kв„Ұ,жҜ”еҰӮMAX 485ж•°жҚ®жүӢеҶҢдёәдҫӢпјҡ иҮідәҺдёәд»Җд№ҲжҳҜ32дёӘе‘ўпјҹдё»иҰҒжҳҜз”ұдәҺеүҚйқў200mVжңҖе°Ҹй©ұеҠЁиғҪеҠӣзҡ„规е®ҡгҖӮд№ҹеҸҜд»Ҙиҝҷж ·зҗҶи§ЈдёҖдёӢпјҢжҜҸдёҖдёӘжҺҘ收з”өи·Ҝиҫ“е…Ҙйҳ»жҠ—并йқһзҗҶжғізҡ„й«ҳйҳ»пјҢиҖҢжҳҜ12kв„ҰпјҢйӮЈд№ҲжҜ”еҰӮе…¶дёӯдёҖдёӘз«ҷзӮ№еҸ‘йҖҒпјҢе°ұзӣёеҪ“дәҺжңү32дёӘз«ҷзӮ№зҡ„иҫ“е…Ҙйҳ»жҠ—并иҒ”пјҢдёәд»Җд№ҲжҳҜ32дёӘе‘ўпјҹеҲ«еҝҳдәҶеҸ‘йҖҒз«ҷзӮ№иҮӘиә«д№ҹжңүжҺҘ收з”өи·ҜпјҢжүҖд»ҘеңЁдёҚиҖғиҷ‘з«ҜжҺҘз”өйҳ»д»ҘеҸҠзәҝи·Ҝйҳ»жҠ—зҡ„жғ…еҶөдёӢпјҢеҜ№дәҺеҸ‘йҖҒз”өи·ҜжҺҘдәҶдёҖдёӘзӯүж•ҲиҙҹиҪҪпјҡпјҢиҖҢеҸ‘йҖҒз”өи·Ҝй©ұеҠЁиғҪеҠӣиӮҜе®ҡжҳҜжңүйҷҗзҡ„пјҢиҝҷж ·е°ұеҘҪзҗҶи§ЈдәҶгҖӮдёӢйқўиҝҷдёӘеӣҫе°ұжҳҜжүҖи°“зҡ„еӨҡзӮ№зҪ‘з»ңжӢ“жү‘пјҢжүҖжңүзҡ„з«ҷзӮ№йғҪжҳҜжІҝзқҖеҸҢз»һзәҝзҡ„жҺ’еёғ并жҺҘеңЁжҖ»зәҝдёҠзҡ„гҖӮ

иҮідәҺдёәд»Җд№ҲжҳҜ32дёӘе‘ўпјҹдё»иҰҒжҳҜз”ұдәҺеүҚйқў200mVжңҖе°Ҹй©ұеҠЁиғҪеҠӣзҡ„规е®ҡгҖӮд№ҹеҸҜд»Ҙиҝҷж ·зҗҶи§ЈдёҖдёӢпјҢжҜҸдёҖдёӘжҺҘ收з”өи·Ҝиҫ“е…Ҙйҳ»жҠ—并йқһзҗҶжғізҡ„й«ҳйҳ»пјҢиҖҢжҳҜ12kв„ҰпјҢйӮЈд№ҲжҜ”еҰӮе…¶дёӯдёҖдёӘз«ҷзӮ№еҸ‘йҖҒпјҢе°ұзӣёеҪ“дәҺжңү32дёӘз«ҷзӮ№зҡ„иҫ“е…Ҙйҳ»жҠ—并иҒ”пјҢдёәд»Җд№ҲжҳҜ32дёӘе‘ўпјҹеҲ«еҝҳдәҶеҸ‘йҖҒз«ҷзӮ№иҮӘиә«д№ҹжңүжҺҘ收з”өи·ҜпјҢжүҖд»ҘеңЁдёҚиҖғиҷ‘з«ҜжҺҘз”өйҳ»д»ҘеҸҠзәҝи·Ҝйҳ»жҠ—зҡ„жғ…еҶөдёӢпјҢеҜ№дәҺеҸ‘йҖҒз”өи·ҜжҺҘдәҶдёҖдёӘзӯүж•ҲиҙҹиҪҪпјҡпјҢиҖҢеҸ‘йҖҒз”өи·Ҝй©ұеҠЁиғҪеҠӣиӮҜе®ҡжҳҜжңүйҷҗзҡ„пјҢиҝҷж ·е°ұеҘҪзҗҶи§ЈдәҶгҖӮдёӢйқўиҝҷдёӘеӣҫе°ұжҳҜжүҖи°“зҡ„еӨҡзӮ№зҪ‘з»ңжӢ“жү‘пјҢжүҖжңүзҡ„з«ҷзӮ№йғҪжҳҜжІҝзқҖеҸҢз»һзәҝзҡ„жҺ’еёғ并жҺҘеңЁжҖ»зәҝдёҠзҡ„гҖӮ жүҖд»ҘпјҢдҪ жңүеҸҜиғҪдјҡеңЁдёҖдәӣең°ж–№зңӢеҲ°жүҖи°“зҡ„дёҖдёӘеҚ•дҪҚRS-485иҙҹиҪҪзҡ„иҜҙжі•пјҢиҝҷйҮҢжүҖи°“зҡ„еҚ•дҪҚиҙҹиҪҪе°ұжҳҜжҢҮ12kв„Ұж ҮеҮҶиҫ“е…Ҙйҳ»жҠ—пјҢиҝҷдёӘ12kв„Ұе°ұжҳҜEIA-485ж ҮеҮҶе®ҡд№үзҡ„гҖӮд»ҺиҖҢзңӢеҲ°жҜ”еҰӮ еҚ•дҪҚиҙҹиҪҪд№Ӣзұ»зҡ„иҜҙжі•пјҢе°ұжҳҜжәҗдәҺжӯӨеӨ„гҖӮ

жүҖд»ҘпјҢдҪ жңүеҸҜиғҪдјҡеңЁдёҖдәӣең°ж–№зңӢеҲ°жүҖи°“зҡ„дёҖдёӘеҚ•дҪҚRS-485иҙҹиҪҪзҡ„иҜҙжі•пјҢиҝҷйҮҢжүҖи°“зҡ„еҚ•дҪҚиҙҹиҪҪе°ұжҳҜжҢҮ12kв„Ұж ҮеҮҶиҫ“е…Ҙйҳ»жҠ—пјҢиҝҷдёӘ12kв„Ұе°ұжҳҜEIA-485ж ҮеҮҶе®ҡд№үзҡ„гҖӮд»ҺиҖҢзңӢеҲ°жҜ”еҰӮ еҚ•дҪҚиҙҹиҪҪд№Ӣзұ»зҡ„иҜҙжі•пјҢе°ұжҳҜжәҗдәҺжӯӨеӨ„гҖӮж•°жҚ®зӣ‘жҺ§

жҜ”еҰӮдёҖдёӘеҹәдәҺRS-485зҡ„Modbus-RTUеӨҡзӮ№зҪ‘з»ңдёӯпјҢеңЁеҒҡеҚҸи®®зј–зЁӢжҲ–иҖ…е®һйҷ…еӨҡз«ҷзӮ№жҖ»зәҝи°ғиҜ•зҡ„ж—¶еҖҷпјҢжңүеҸҜиғҪйңҖиҰҒзӣ‘жҺ§жҖ»зәҝдёҠжүҖжңүзҡ„жҠҘж–ҮгҖӮз”ҡиҮіиҝҳжңүеҸҜиғҪе°ұеғҸе®һзҺ°дёҖдёӘжҖ»зәҝжҠҘж–Үзҡ„зҡ„и®°еҪ•еҷЁпјҢе°ҶжҖ»зәҝдёҠжүҖжңүзҡ„жҠҘж–ҮйғҪи®°еҪ•дёӢжқҘгҖӮеә”иҜҘжҖҺд№Ҳе®һзҺ°е‘ўпјҹд№°дёҖж №USBиҪ¬RS-485зҡ„иҪ¬жҚўзәҝжҲ–иҖ…иҮӘе·ұеҒҡдёҖдёӘд№ҹеҸҜд»ҘгҖӮе°ҶA/Bзәҝ并жҺҘеңЁжҖ»зәҝдёҠпјҢUSB жҸ’е…Ҙз”өи„‘гҖӮдҪҝз”ЁдёІеҸЈзӣ‘жҺ§з»Ҳз«ҜжҲ–иҖ…иҮӘе·ұеҶҷдёҖдёӘдёІеҸЈжҺҘ收е°ҸиҪҜ件пјҢе°ұеҸҜд»Ҙзӣ‘жҺ§жүҖжңүжҖ»зәҝдёҠзҡ„жҠҘж–ҮдәҶгҖӮжҜ”еҰӮиҝҷдёӘAccessPortдёІеҸЈе·Ҙе…·е°ұжҜ”иҫғеҘҪз”Ёпјҡ

еә”з”Ёи®ҫи®Ў

дҪңдёәеә”з”Ёи®ҫи®ЎиҖҢиЁҖпјҢйңҖиҰҒиҖғиҷ‘иҝҷдәӣз»ҙеәҰпјҡ- з«ҜжҺҘи®ҫи®Ў

- жҺҘеҸЈиҠҜзүҮ

- йҡ”зҰ»и®ҫи®Ў

з«ҜжҺҘи®ҫи®Ў

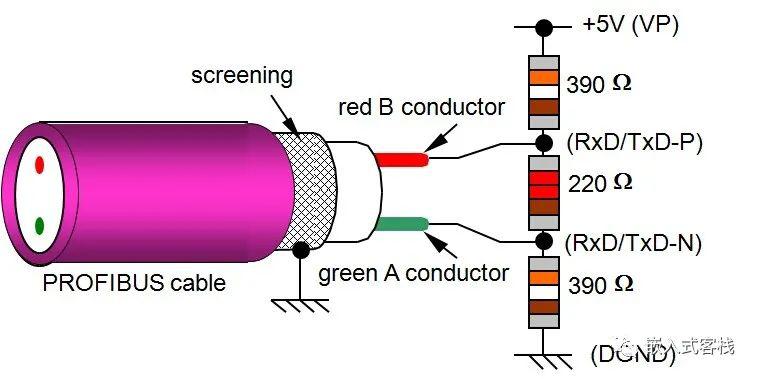

йҰ–е…Ҳдёәд»Җд№ҲиҰҒз«ҜжҺҘпјҹиҝҷжҳҜз”ұдәҺRS-485йҮҮз”ЁеҸҢз»һзәҝдј иҫ“пјҢж ҮеҮҶ规е®ҡзҡ„еҸҢз»һзәҝзҡ„е·®еҲҶзү№еҫҒйҳ»жҠ—еңЁ100О©иҮі150О©д№Ӣй—ҙгҖӮRS-485ж ҮеҮҶеҲ¶е®ҡиҖ…йҖүжӢ©120О©дҪңдёәж Үз§°зү№еҫҒйҳ»жҠ—гҖӮ еҒҮе®ҡдҝЎеҸ·иҮӘе·Ұиҫ№з«ҷзӮ№еҸ‘еҮәпјҢеҰӮжһңжІЎжңүз«ҜжҺҘпјҢдҝЎеҸ·еңЁзәҝи·ҜдёҠдј иҫ“е…¶йҳ»жҠ—жҳҜиҝһз»ӯзҡ„пјҢдҪҶжҳҜеҲ°иҫҫеҸідҫ§зҡ„ж—¶еҖҷеҲҷпјҢзӯүж•Ҳйҳ»жҠ—еҸҳжҲҗдәҶжҺҘ收з”өи·Ҝзҡ„иҫ“е…Ҙйҳ»жҠ—пјҢжҜ”еҰӮжҳҜ12kО©пјҢйҳ»жҠ—дёҚиҝһз»ӯдәҶпјҢйҳ»жҠ—зӘҒеҸҳпјҒдҝЎеҸ·зҡ„дёҖйғЁеҲҶиғҪйҮҸе°ұдјҡжҢүз…§еҺҹи·Ҝеҫ„иҝ”еӣһпјҢеҰӮиҝ”еӣһеӣһеҺ»зҡ„дҝЎеҸ·з”ұдәҺе®№жҠ—еҸҠж„ҹжҠ—пјҢе°ұдјҡдә§з”ҹзӣёе·®гҖӮеҸҚе°„еӣһеҺ»зҡ„дҝЎеҸ·дёҺеҺҹдҝЎеҸ·еҸ еҠ еңЁдёҖиө·гҖӮиҝҷж ·е°ұдјҡйҖ жҲҗйҖҡдҝЎеҸ‘з”ҹй”ҷиҜҜпјҢдёҘйҮҚзҡ„ж—¶еҖҷпјҢйҖҡдҝЎе°ұж— жі•жӯЈзЎ®иҝӣиЎҢгҖӮиҰҒжғіжӣҙж·ұе…Ҙзҡ„дәҶи§ЈиғҢеҗҺзҡ„еҺҹзҗҶпјҢеҸҜд»ҘеҺ»еӯҰд№ дёҖдёӢдј иҫ“зәҝзҗҶи®әгҖӮжҲ–и®ёеҒҡиҝҮProfibus DPпјҲзү©зҗҶеұӮд№ҹжҳҜйҮҮз”Ёзҡ„RS-485пјүзҡ„жңӢеҸӢдјҡиҜҙпјҢдҪ зңӢprofibus DPдёәд»Җд№ҲжҺЁиҚҗзҡ„з»Ҳз«ҜеҢ№й…Қз”өи·ҜжҳҜдёӢйқўиҝҷж ·зҡ„е‘ўпјҹ

еҒҮе®ҡдҝЎеҸ·иҮӘе·Ұиҫ№з«ҷзӮ№еҸ‘еҮәпјҢеҰӮжһңжІЎжңүз«ҜжҺҘпјҢдҝЎеҸ·еңЁзәҝи·ҜдёҠдј иҫ“е…¶йҳ»жҠ—жҳҜиҝһз»ӯзҡ„пјҢдҪҶжҳҜеҲ°иҫҫеҸідҫ§зҡ„ж—¶еҖҷеҲҷпјҢзӯүж•Ҳйҳ»жҠ—еҸҳжҲҗдәҶжҺҘ收з”өи·Ҝзҡ„иҫ“е…Ҙйҳ»жҠ—пјҢжҜ”еҰӮжҳҜ12kО©пјҢйҳ»жҠ—дёҚиҝһз»ӯдәҶпјҢйҳ»жҠ—зӘҒеҸҳпјҒдҝЎеҸ·зҡ„дёҖйғЁеҲҶиғҪйҮҸе°ұдјҡжҢүз…§еҺҹи·Ҝеҫ„иҝ”еӣһпјҢеҰӮиҝ”еӣһеӣһеҺ»зҡ„дҝЎеҸ·з”ұдәҺе®№жҠ—еҸҠж„ҹжҠ—пјҢе°ұдјҡдә§з”ҹзӣёе·®гҖӮеҸҚе°„еӣһеҺ»зҡ„дҝЎеҸ·дёҺеҺҹдҝЎеҸ·еҸ еҠ еңЁдёҖиө·гҖӮиҝҷж ·е°ұдјҡйҖ жҲҗйҖҡдҝЎеҸ‘з”ҹй”ҷиҜҜпјҢдёҘйҮҚзҡ„ж—¶еҖҷпјҢйҖҡдҝЎе°ұж— жі•жӯЈзЎ®иҝӣиЎҢгҖӮиҰҒжғіжӣҙж·ұе…Ҙзҡ„дәҶи§ЈиғҢеҗҺзҡ„еҺҹзҗҶпјҢеҸҜд»ҘеҺ»еӯҰд№ дёҖдёӢдј иҫ“зәҝзҗҶи®әгҖӮжҲ–и®ёеҒҡиҝҮProfibus DPпјҲзү©зҗҶеұӮд№ҹжҳҜйҮҮз”Ёзҡ„RS-485пјүзҡ„жңӢеҸӢдјҡиҜҙпјҢдҪ зңӢprofibus DPдёәд»Җд№ҲжҺЁиҚҗзҡ„з»Ҳз«ҜеҢ№й…Қз”өи·ҜжҳҜдёӢйқўиҝҷж ·зҡ„е‘ўпјҹ е…¶е®һжҳҜеӣ дёәProfibus DPйҮҮз”Ёзҡ„йҖҡдҝЎд»ӢиҙЁе…¶ж Үз§°зү№еҫҒйҳ»жҠ—дёҚдёҖж ·гҖӮжүҖд»Ҙе®һйҷ…е·ҘзЁӢеә”з”Ёзҡ„ж—¶еҖҷеҲҷдјҡжңүе°Ҹзҡ„е·®ејӮгҖӮ

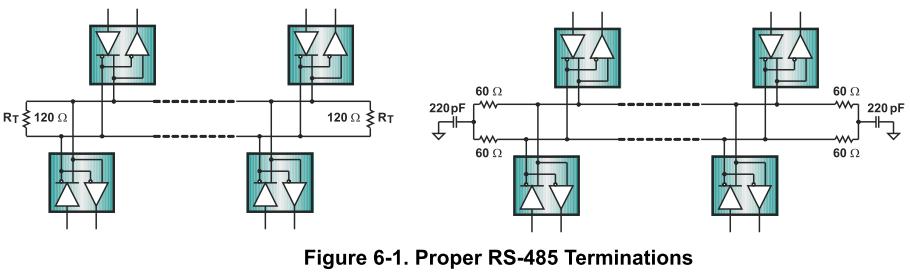

е…¶е®һжҳҜеӣ дёәProfibus DPйҮҮз”Ёзҡ„йҖҡдҝЎд»ӢиҙЁе…¶ж Үз§°зү№еҫҒйҳ»жҠ—дёҚдёҖж ·гҖӮжүҖд»Ҙе®һйҷ…е·ҘзЁӢеә”з”Ёзҡ„ж—¶еҖҷеҲҷдјҡжңүе°Ҹзҡ„е·®ејӮгҖӮеңЁTIзҡ„иө„ж–ҷдёҠзңӢеҲ°иҝҷж ·дёҖдёӘз«ҜжҺҘжҺҘжі•пјҡ

еңЁеҷӘеЈ°жҜ”иҫғдёҘйҮҚзҡ„еңәеҗҲпјҢе»әи®®дҪҝз”ЁеҸіиҫ№зҡ„з«ҜжҺҘж–№жЎҲпјҢеҲ©з”ЁдёӨдёӘ60О©з”өйҳ»д»ҘеҸҠ220pFз”өе®№еҪўжҲҗдҪҺйҖҡж»ӨжіўеҷЁпјҢе°ҶеўһеҠ зәҝи·Ҝзҡ„жҠ—еҷӘеЈ°иғҪеҠӣгҖӮеңЁе®һйҷ…е·ҘзЁӢеёғзәҝзҡ„ж—¶еҖҷпјҢеҰӮжһңйҒҮеҲ°еҷӘеЈ°жҜ”иҫғдёҘйҮҚзҡ„ж—¶еҖҷпјҢдёҖж–№йқўеҸҜд»ҘеҲ©з”ЁзӨәжіўеҷЁжҹҘзңӢжҖ»зәҝдҝЎеҸ·иҙЁйҮҸпјҢеңЁе°Ҷз«ҜжҺҘж–№ејҸеҒҡдёҖдәӣе°Ҹзҡ„и°ғж•ҙгҖӮ

еңЁеҷӘеЈ°жҜ”иҫғдёҘйҮҚзҡ„еңәеҗҲпјҢе»әи®®дҪҝз”ЁеҸіиҫ№зҡ„з«ҜжҺҘж–№жЎҲпјҢеҲ©з”ЁдёӨдёӘ60О©з”өйҳ»д»ҘеҸҠ220pFз”өе®№еҪўжҲҗдҪҺйҖҡж»ӨжіўеҷЁпјҢе°ҶеўһеҠ зәҝи·Ҝзҡ„жҠ—еҷӘеЈ°иғҪеҠӣгҖӮеңЁе®һйҷ…е·ҘзЁӢеёғзәҝзҡ„ж—¶еҖҷпјҢеҰӮжһңйҒҮеҲ°еҷӘеЈ°жҜ”иҫғдёҘйҮҚзҡ„ж—¶еҖҷпјҢдёҖж–№йқўеҸҜд»ҘеҲ©з”ЁзӨәжіўеҷЁжҹҘзңӢжҖ»зәҝдҝЎеҸ·иҙЁйҮҸпјҢеңЁе°Ҷз«ҜжҺҘж–№ејҸеҒҡдёҖдәӣе°Ҹзҡ„и°ғж•ҙгҖӮжҺҘеҸЈи®ҫи®Ў

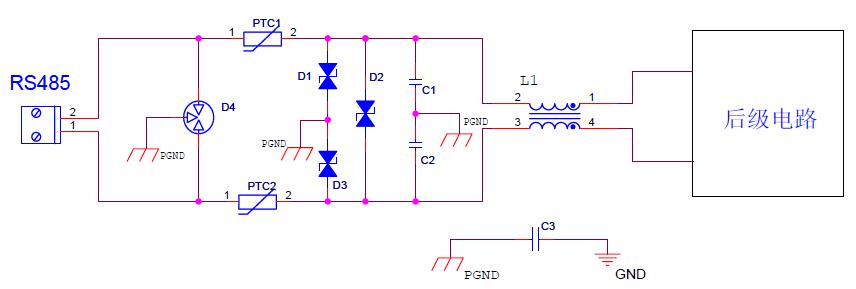

RS-485收еҸ‘еҷЁиҠҜзүҮеҫҲеӨҡиҠҜзүҮе…¬еҸёйғҪжҸҗдҫӣпјҢжҜ”еҰӮTI,Microchip зӯүеҺӮ家йғҪжңүпјҢйҖүжӢ©жҺҘеҸЈиҠҜзүҮзҡ„ж—¶еҖҷйңҖиҰҒиҖғиҷ‘пјҢиҠҜзүҮзҡ„дҫӣз”өз”өеҺӢиҫ“е…ҘйҖ»иҫ‘жҳҜеҗҰдёҺдҪҝз”Ёзҡ„еҚ•зүҮжңә/DSPзҡ„з”өе№іе…је®№пјҢеҸҰеӨ–е°ұжҳҜеүҚйқўжҸҗеҲ°зҡ„е…¶жҺҘ收з”өи·Ҝзҡ„йҳ»жҠ—жҳҜеҗҰжҳҜз¬ҰеҗҲRS-485ж ҮеҮҶиҫ“е…Ҙйҳ»жҠ—зҡ„гҖӮеҰӮжһңдёҚжҳҜзҡ„пјҢйӮЈд№ҲеңЁиҖғиҷ‘зҪ‘з»ңйғЁзҪІзҡ„ж—¶еҖҷпјҢжүҖиғҪеёҰзҡ„иҙҹиҪҪж•°йҮҸе°ұжңүеҸҜиғҪйңҖиҰҒеҒҡи°ғж•ҙгҖӮеҸҰеӨ–жіЁж„ҸдёҖдёӢпјҢжңүзҡ„ж–°и®ҫи®ЎRS-485收еҸ‘еҷЁе…·еӨҮfail-safeеҠҹиғҪгҖӮеҸҰеӨ–пјҢеүҚйқўиҜҙеҲ°ж ҮеҮҶ收еҸ‘еҷЁеҸҜд»Ҙй©ұеҠЁ32дёӘж ҮеҮҶ收еҸ‘еҷЁиҙҹиҪҪи®ҫеӨҮпјҢд№ҹеҚіжҳҜпјҲ12kО©)ж ҮеҮҶеҚ•дҪҚиҫ“е…Ҙйҳ»жҠ—гҖӮеңЁеҒҡе…·дҪ“жҺҘеҸЈз”өи·Ҝи®ҫи®Ўзҡ„ж—¶еҖҷиҝҳйңҖиҰҒиҖғиҷ‘EMCиҰҒжұӮпјҢеңЁдёҖдәӣи®ҫеӨҮзҺ°еңәзңҹзҡ„жңүеҫҲејәзҡ„е№Іжү°пјҢжҜ”еҰӮз”өзҪ‘дёҠжңүеӨ§зҡ„з”өжңәзӯүж„ҹжҖ§и®ҫеӨҮиҝҗиЎҢпјҢжңүж—¶еҖҷе°ұдјҡе№Іжү°и®ҫеӨҮпјӣеҸҰеӨ–д№ҹжңүеҸҜиғҪжңүз©әй—ҙиҫҗе°„е№Іжү°пјҢиҝҷж—¶еҖҷеҸҜд»ҘиҖғиҷ‘йҮҮз”ЁеёҰеұҸи”ҪеҸҢз»һзәҝпјҢеұҸи”ҪеұӮжҺҘеӨ§ең°пјҢжҠ—е№Іжү°ж–№йқўжҲ‘дәҶи§Јзҡ„дёҚжҳҜеҫҲж·ұе…ҘпјҢд»…ж•ҙзҗҶдёҖдёӢгҖӮеңЁиҝҷйҮҢзңӢеҲ°дёҖдёӘйҳІйӣ·жҺҘеҸЈз”өи·Ҝзҡ„и®ҫи®Ўж–№жЎҲпјҢеҸҜд»ҘеҸӮиҖғдёҖдёӢпјҡ https://www.programmersought.com/article/95833359295/еүҚйқўиҜҙйҖҡеёёж ҮеҮҶRS-485еҸҜд»Ҙе®№зәі32дёӘж ҮеҮҶжҺҘ收йҳ»жҠ—收еҸ‘и®ҫеӨҮгҖӮе®һйҷ…зі»з»ҹдёӯе°ұжҳҜжғіжҺҘе…Ҙи¶…иҝҮ32дёӘз«ҷзӮ№и®ҫеӨҮпјҢжҖҺд№ҲеҠһе‘ўпјҹеҸҜд»Ҙи®ҫи®ЎдёҖдёӘдёӯ继и®ҫеӨҮгҖӮжғіеҪ“дәҺе°ҶдёӨдёӘзҪ‘ж®өеҲ©з”Ёдёӯ继з»ҷиЎ”жҺҘиө·жқҘпјҢд»Ҙи§ЈеҶій©ұеҠЁиғҪеҠӣдёҚи¶ізҡ„й—®йўҳгҖӮеҪ“然д№ҹжңүиҝҷж ·зҡ„зҺ°жҲҗдә§е“ҒгҖӮ

https://www.programmersought.com/article/95833359295/еүҚйқўиҜҙйҖҡеёёж ҮеҮҶRS-485еҸҜд»Ҙе®№зәі32дёӘж ҮеҮҶжҺҘ收йҳ»жҠ—收еҸ‘и®ҫеӨҮгҖӮе®һйҷ…зі»з»ҹдёӯе°ұжҳҜжғіжҺҘе…Ҙи¶…иҝҮ32дёӘз«ҷзӮ№и®ҫеӨҮпјҢжҖҺд№ҲеҠһе‘ўпјҹеҸҜд»Ҙи®ҫи®ЎдёҖдёӘдёӯ继и®ҫеӨҮгҖӮжғіеҪ“дәҺе°ҶдёӨдёӘзҪ‘ж®өеҲ©з”Ёдёӯ继з»ҷиЎ”жҺҘиө·жқҘпјҢд»Ҙи§ЈеҶій©ұеҠЁиғҪеҠӣдёҚи¶ізҡ„й—®йўҳгҖӮеҪ“然д№ҹжңүиҝҷж ·зҡ„зҺ°жҲҗдә§е“ҒгҖӮйҡ”зҰ»и®ҫи®Ў

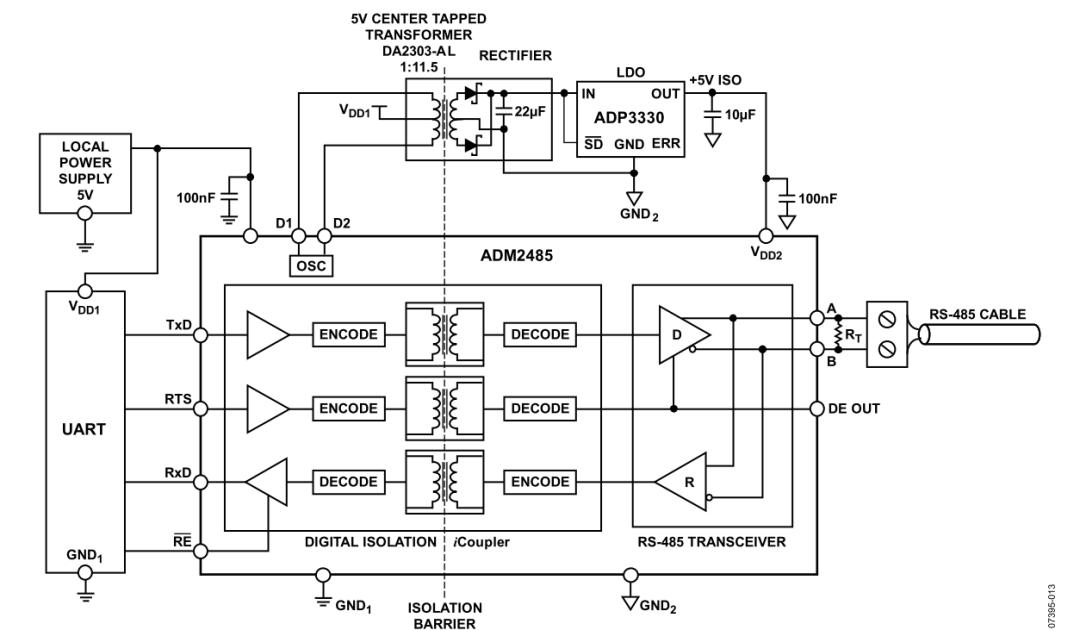

дёәд»Җд№ҲиҰҒйҡ”зҰ»пјҢжҳҜдёәдәҶйҷҚдҪҺжҺҘең°еҷӘеЈ°гҖӮеңЁеҫҲеӨҡзҺ°еңәеҸҜиғҪжңүеӨ§з”өжөҒејҖе…іи®ҫеӨҮпјҢз”өжңәж„ҹжҖ§и®ҫеӨҮзӯүпјҢеҷӘеЈ°еҫҲжңүеҸҜиғҪйҖҡиҝҮйҖҡи®Ҝзҡ„жҺҘең°иҖҰеҗҲиҝӣи®ҫеӨҮгҖӮе°Өе…¶еңЁе·Ҙдёҡи®ҫеӨҮдёӯпјҢдёҖиҲ¬йғҪдјҡи®ҫи®ЎжҲҗеёҰйҡ”зҰ»зҡ„жҺҘеҸЈз”өи·ҜгҖӮиҰҒи®ҫи®Ўйҡ”зҰ»жҺҘеҸЈпјҢеҸҜд»ҘиҖғиҷ‘йҖүжӢ©е…·жңүйҡ”зҰ»еҠҹиғҪзҡ„иҠҜзүҮпјҢжҜ”еҰӮADIзҡ„ iCouplerжҠҖжңҜдә§е“ҒADM2481пјҢADM2485гҖӮеҪ“然д№ҹеҸҜд»ҘйҮҮз”Ёе…үиҖҰ+жҷ®йҖҡRS-485收еҸ‘еҷЁзҡ„ж–№ејҸгҖӮе”ҜдёҖйңҖиҰҒжіЁж„Ҹзҡ„жҳҜйңҖиҰҒи®ҫи®ЎдёҖдёӘеёҰйҡ”зҰ»зҡ„з”өжәҗпјҢз»ҷйҡ”зҰ»дёӨдҫ§з”өи·ҜеҲҶеҲ«дҫӣз”өгҖӮ дёҠйқўиҝҷдёӘеӣҫжқҘиҮӘTIзҡ„гҖҠThe RS-485 Design GuideгҖӢпјҢиҝҷд»Ҫиө„ж–ҷж„ҹи§үеҫҲдёҚй”ҷпјҢжң¬ж–ҮеҫҲеӨҡең°ж–№д№ҹеҸӮиҖғиҝҷд»Ҫж–ҮжЎЈж•ҙзҗҶзҡ„гҖӮеҰӮеҜ№иҝҷд»Ҫиө„ж–ҷжңүе…ҙи¶ЈпјҢеҸҜд»ҘеңЁеҗҺеҸ°еӣһеӨҚ485иҮӘеҠЁйўҶеҸ–гҖӮ

дёҠйқўиҝҷдёӘеӣҫжқҘиҮӘTIзҡ„гҖҠThe RS-485 Design GuideгҖӢпјҢиҝҷд»Ҫиө„ж–ҷж„ҹи§үеҫҲдёҚй”ҷпјҢжң¬ж–ҮеҫҲеӨҡең°ж–№д№ҹеҸӮиҖғиҝҷд»Ҫж–ҮжЎЈж•ҙзҗҶзҡ„гҖӮеҰӮеҜ№иҝҷд»Ҫиө„ж–ҷжңүе…ҙи¶ЈпјҢеҸҜд»ҘеңЁеҗҺеҸ°еӣһеӨҚ485иҮӘеҠЁйўҶеҸ–гҖӮжҖ»з»“дёҖдёӢ

RS-485зңӢдјјз®ҖеҚ•пјҢе®һйҷ…еә”з”Ёи®ҫи®Ўзҡ„ж—¶еҖҷиҝҳжҳҜжңүеҫҲеӨҡйңҖиҰҒеҺ»зҗҶи§Је’ҢжіЁж„Ҹзҡ„ең°ж–№гҖӮеҒҡдёҖдёӘзЁіеҒҘзҡ„дә§е“ҒпјҢеҫҖеҫҖжүҖе·®дёҚжҳҜеӨ§ж–№еҗ‘пјҢиҖҢжҳҜдёҖдәӣз»Ҷеҫ®еӨ„е®№жҳ“еҜјиҮҙдә§е“ҒдёҚзЁіе®ҡгҖӮжҺЁиҚҗе…іжіЁ????дёӢж–№е…¬дј—еҸ·еӯҰд№ жӣҙеӨҡз”өеӯҗжҠҖжңҜзҹҘиҜҶпјҒ